Displays, Andpsi121ga0s-hb-kit – Purdy ANDpSi121GAOS-HB-KIT User Manual

Page 3

Purdy Electronics Corporation • 720 Palomar Avenue • Sunnyvale, CA 94085

7/27/07

Tel: 408.523.8216 • Fax: 408.733.1287 •

3

www.purdyelectronics.com

Displays

Notes:

Refer to “Timing Chart” below. If DE is fixed to “H” or “L” level for certain period while NCLK is supplied, the panel displays black w/some flicker.

If NCLK is fixed to “H” or “L” level for certain period while DE is supplied, the panel may be damaged. Please adjust LCD operating signal timing and FL

driving frequency, to optimize the display quality. There is a possibility that flicker is observed by the interference of LCD operating signal timing and

FL driving condition (especially driving frequency), even if the condition satisfies above timing specifications and recommended operating condi-

tions. Do not make

t

v

,

t

vhd and

t

vds fluctuate. If

t

v,

t

vhd, and

t

vds are fluctuate, the panel display black. In case of using the long frame period, the

deterioration of display quality, noise, etc. may be occurred. NCLK count of each Horizontal Scanning Time should be always the same. V-Blanking

period should be ‘n’ X “Horizontal Scanning Time”. (n:integer) Frame period should be always the same.

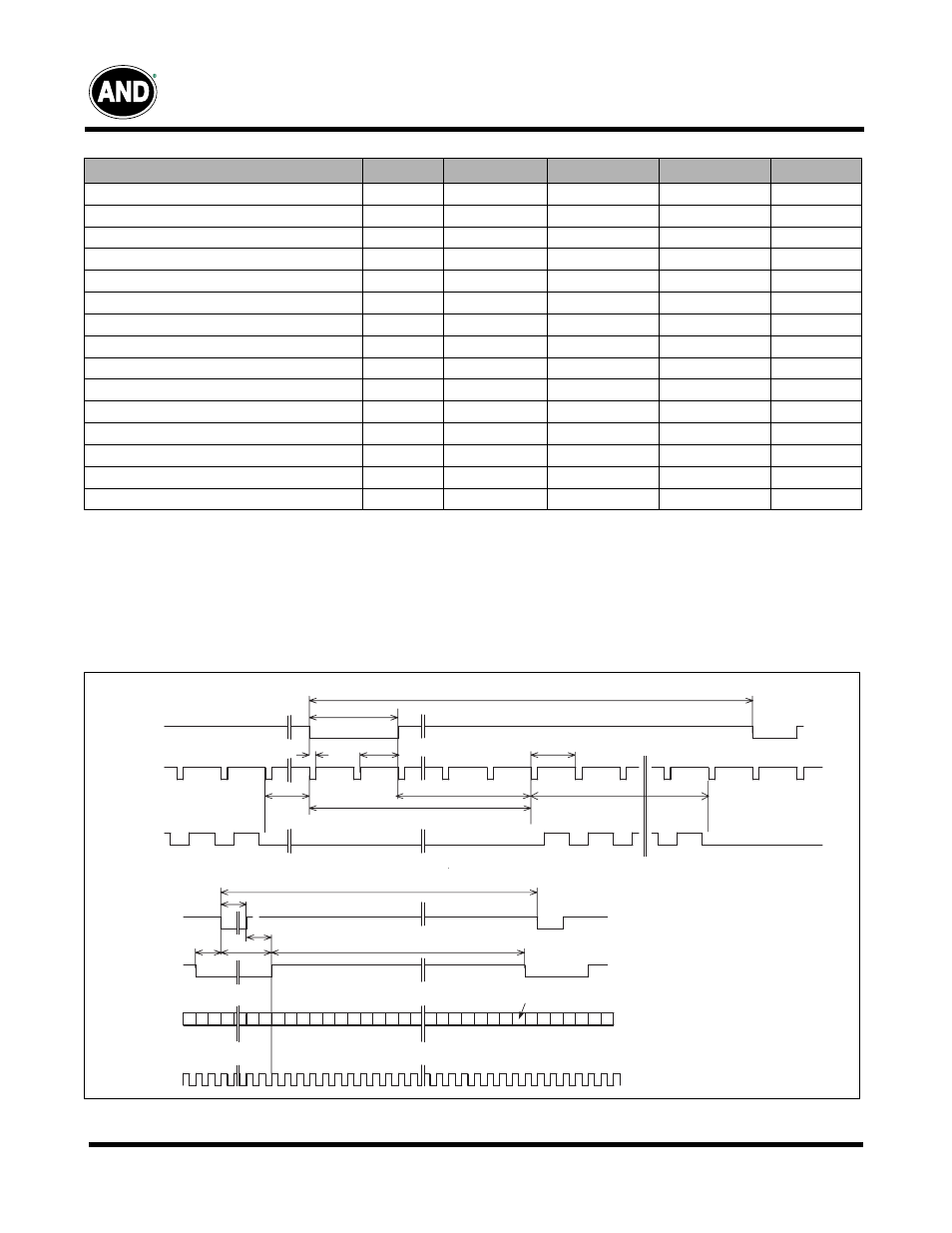

Timing Chart

Timing Specifications

(see Notes below)

Item

Symbol

Min

Typ

Max

Unit

Horizontal Scanning Term

t

h

1334 x

t

c

1344 x

t

c

–

clock

H-sync Pulse Width

t

hw

4 x

t

c

136 x

t

c

–

clock

Horizontal Front Porch

t

hfp

4 x

t

c

24 x

t

c

–

clock

Horizontal Back Porch

t

hbp

24 x

t

c

160 x

t

c

–

clock

Horizontal Data Sync Period

t

hds

32 x

t

c

296 x

t

c

–

clock

Horizontal Display Term

t

hd

1024 x

t

c

1024 x

t

c

1024 x

t

c

clock

Frame Period

t

v

778 x

t

h

806 x

t

h

860 x

t

h

line

V-sync Pulse Width

t

vw

2 x

t

h

6 x

t

h

–

line

V-sync Set up Time (to H-sync)

t

vsu

8 x

t

c

–

–

clock

V-sync Hold Time

t

vhd

(thbp+16) x

t

c

–

–

clock

Vertical Front Porch

t

vfp

1 x

t

h

3 x

t

h

–

line

Vertical Back Porch

t

vbp

2 x

t

h

29 x

t

h

–

line

Vertical Data Sync Period

t

vds

8 x

t

h

35 x

t

h

–

line

Vertical Display Time

t

vd

768 x

t

h

768 x

t

h

768 x

t

h

line

Clock Period

t

c

15.0

15.38

–

ns

tv

tvw

VSYNC

tvsu

tvhd

th

HSYNC

tv p

tvbp

tvd

tvds

DE

1023

1024

1

2

th

thw

HSYNC

thbp

thfp

thds

thd

DE

1024

pixel

CLK

2

3

4

1

ANDpSi121GA0S-HB-KIT