Config & nmi, Config register – Sundance SMT365 User Manual

Page 16

Version 2.3

Page 16 of 28

SMT365 User Manual

CONFIG & NMI

The TIM specification describes the operation of an open-collector type signal

CONFIG that is driven low after reset.

This signal, on a standard C4x based TIM, is connected to the processor’s IIOF3 pin.

On the SMT365, the CONFIG signal is asserted after power on, and can be released

by writing the value (1<<6) to the config register. Conversely, CONFIG may be re-

asserted by writing 0 to this bit. It is not possible for software to read the state of the

CONFIG signal.

The NMI signal from the TIM connector can be routed to the DSP NMI pin.

WARNING:

Several software components include code sequences that assume

setting GIE=0 in the DSP CSR will inhibit all interrupts; NMI violates that assumption.

If an NMI occurs during such code sequences it may not be safe to return from the

interrupt. This may be particularly significant if you are using the compiler’s software

pipelining facility.

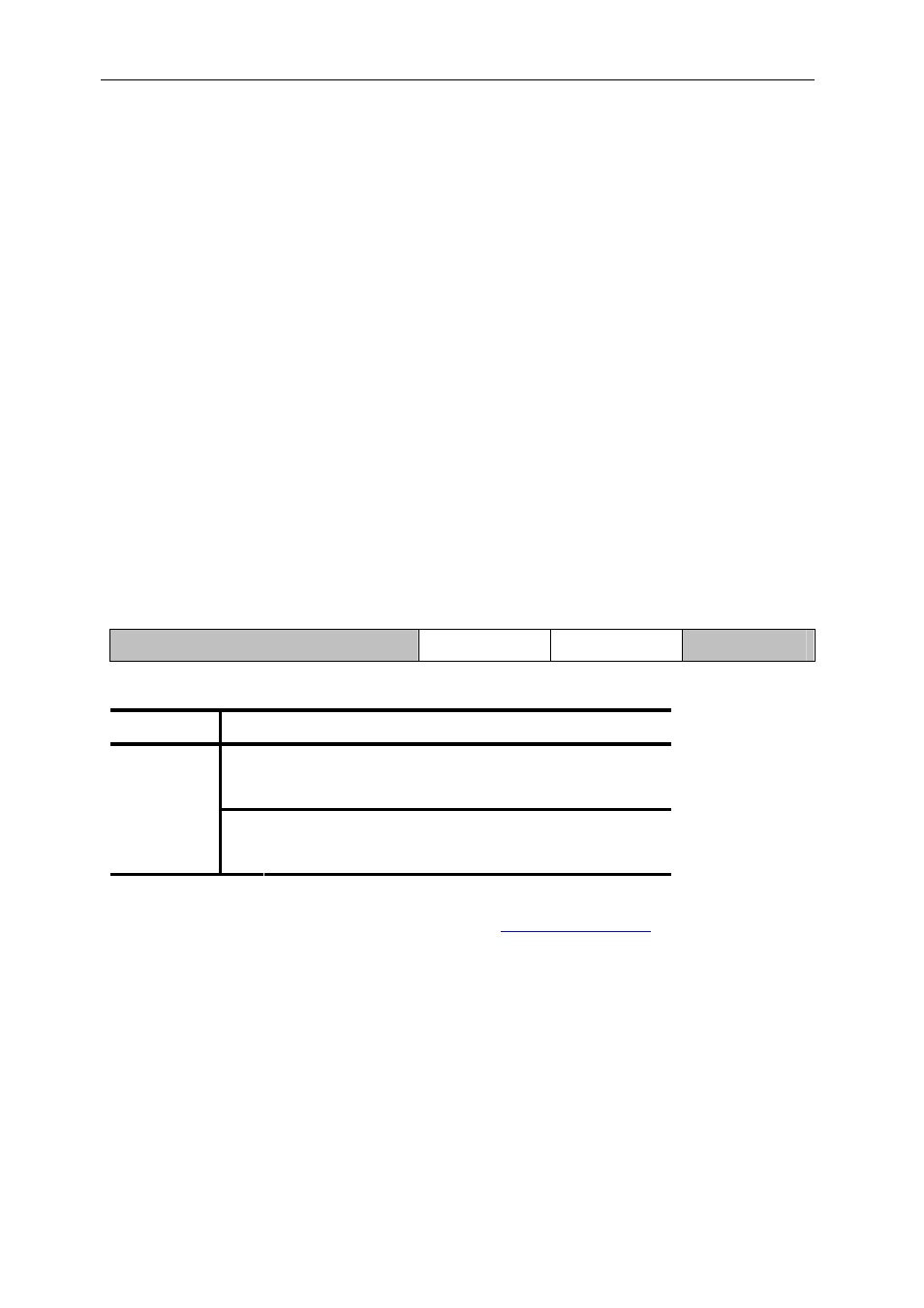

Config Register

31–8 7

6

5–0

NMI

CONFIG

Field Description

0

drive CONFIG low

CONFIG

1 tri-state

CONFIG

0

Disconnect NMI from the DSP

NMI

1

Connect NMI from TIM to the DSP.

Config and NMI DSP lines are described in the