Clock enable, Clock source – Sundance SMT356 User Manual

Page 16

Version 2.1

Page 16 of 26

SMT356356 User Manual

Clock Enable

The clock enable (ADC sample enable) is controlled from either the external enable

input or from an enable register. The selection is made as follows,

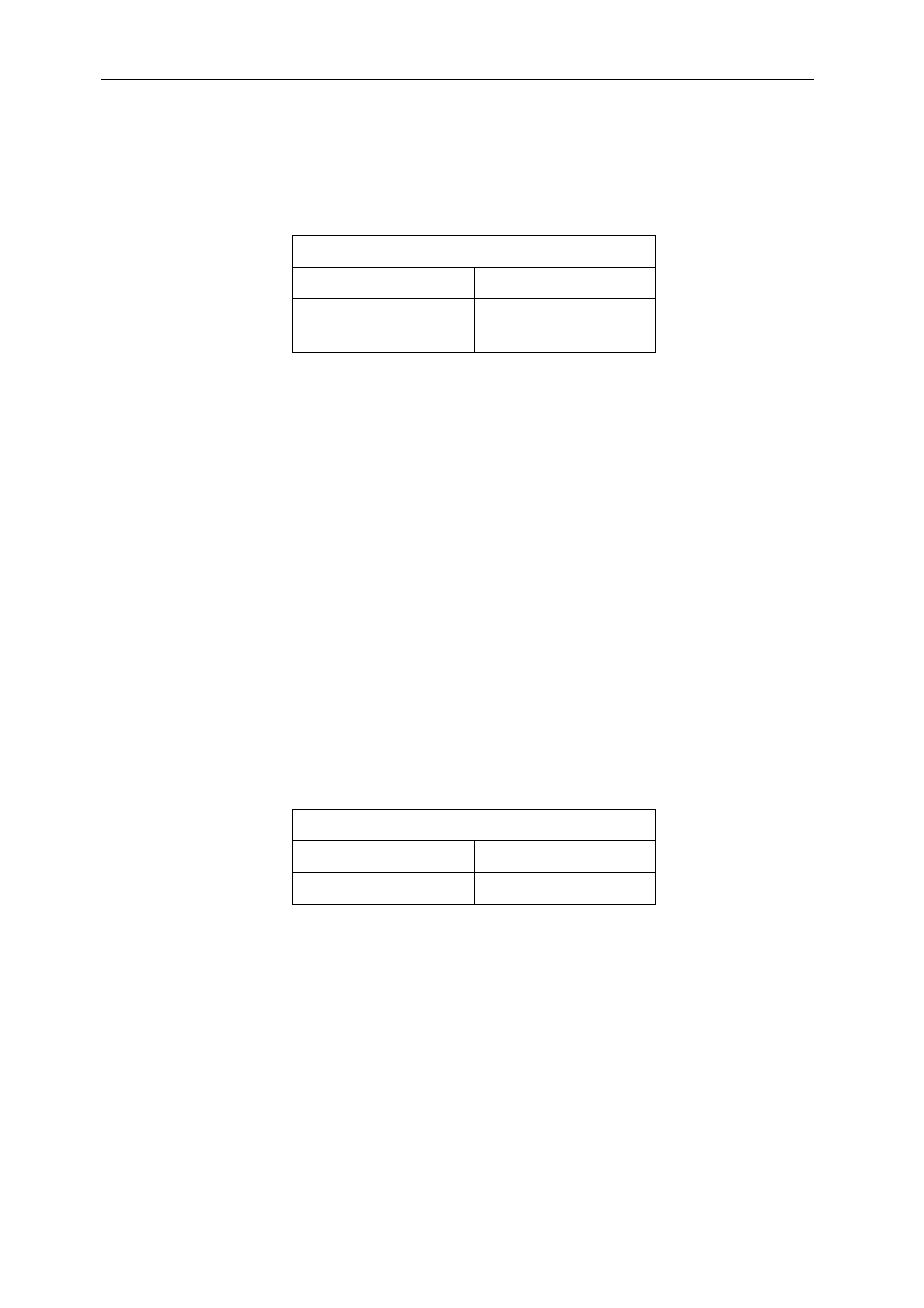

JP1 – position 2

OFF ON

External enable

Internal enable

register

The external enable input has a pull-up resistor to the active state. So, if the module

was to be permanently enabled, then Jumper Bank-2 should be in the ON position

and the clock enable input left unconnected.

The clock enable mode is selected by bit D21 of the control register. With this bit set

to ‘0’, the external clock enable rising edge is used to start a counter which in turn

allows the ADC to be enabled for a pre-set number of samples. The sample count is

set in the control register bits D31-24. If control register bit D21 is set to '1’, then the

external clock enable is routed directly to the ADC and samples will therefore be

taken so long as this signal remains active (‘1’). This is shown diagrammatically in the

following figure.

Clock Source

The sample rate of the converters is derived from one of two sources. Either from an

external clock input or via the on-module reference. The selection is made as follows,

JP1 – position 1

OFF ON

External clock

Internal clock

The maximum external clock frequency is 10MHz. This should be TTL compatible.

In either mode, the selected clock is passed through a programmable divider and

then output to a connector.