Firmware – Sundance SMT145 User Manual

Page 13

Version 1.1

Page 13 of 18

SMT145 User Manual

Firmware

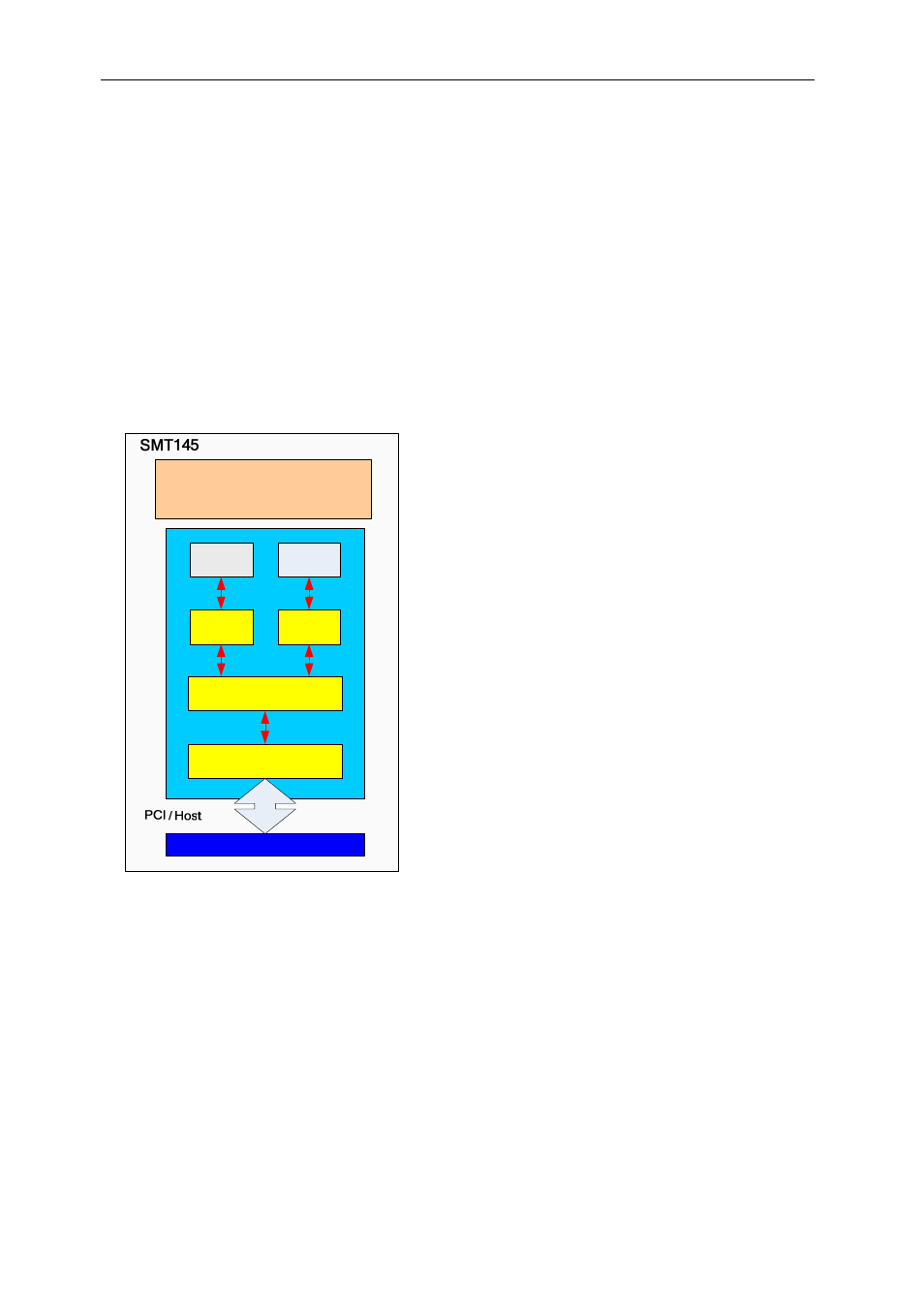

This section deals with the design of the FPGA available on-board the SMT145.

The firmware implements the communication interfaces required to allow the data

transfer between the SMT145 and the TIM and the SMT145 and the PCI.

The host transfers data with the TIM using the X-Link. There is one X-Link

instantiated per communication resource (SHB, RSL). All the X-link are connected to

the PCI core and can be accessed from the host. The default firmware provides two

communication resources: one comport and one RSL. Refer to the SMT6400 and

SMT6500 for more information concerning the communication resources.

A PCI core is used to allow data transfer between the host machine and the X-Link.

32 or 64-bit access

TIM

Comport

RSL

XLink

XLink

DMA

PCI core

FPGA

Figure 3: FPGA design

The PCI core supports target accesses and initiator accesses. Data transfers are

implemented using initiator accesses to ensure maximum bandwidth. For this

purpose a DMA engine is connected to the X-Link and the PCI core to transfer the

data.