6 core assumptions, 7 resources usage and performance, 8 testbench and matlab program – Sundance FC100 User Manual

Page 11: Core assumptions, Resources usage and performance, Testbench and matlab program

6 Core assumptions

Following SYNC_IN, the initial transform has a start-up latency dependent on the bit-reversal

stage, the floating point core latencies and the length of the transform. The core provides

continuous processing at steady state, though the SYNC IN to OUT latencies may vary

slightly due to internal pipeline alignment.

The standard core with transform length of 1024 has a start-up latency of around 2300 clock

cycles, or 9.2usec at 250MHz clock rate.

Latencies of other lengths 2

m

follow approximately the formula:

]}

_

_

)

_

_

2

[(

{

)

2

2

(

)

(

delay

mult

fp

delay

add

fp

m

cycles

clock

in

Latency

m

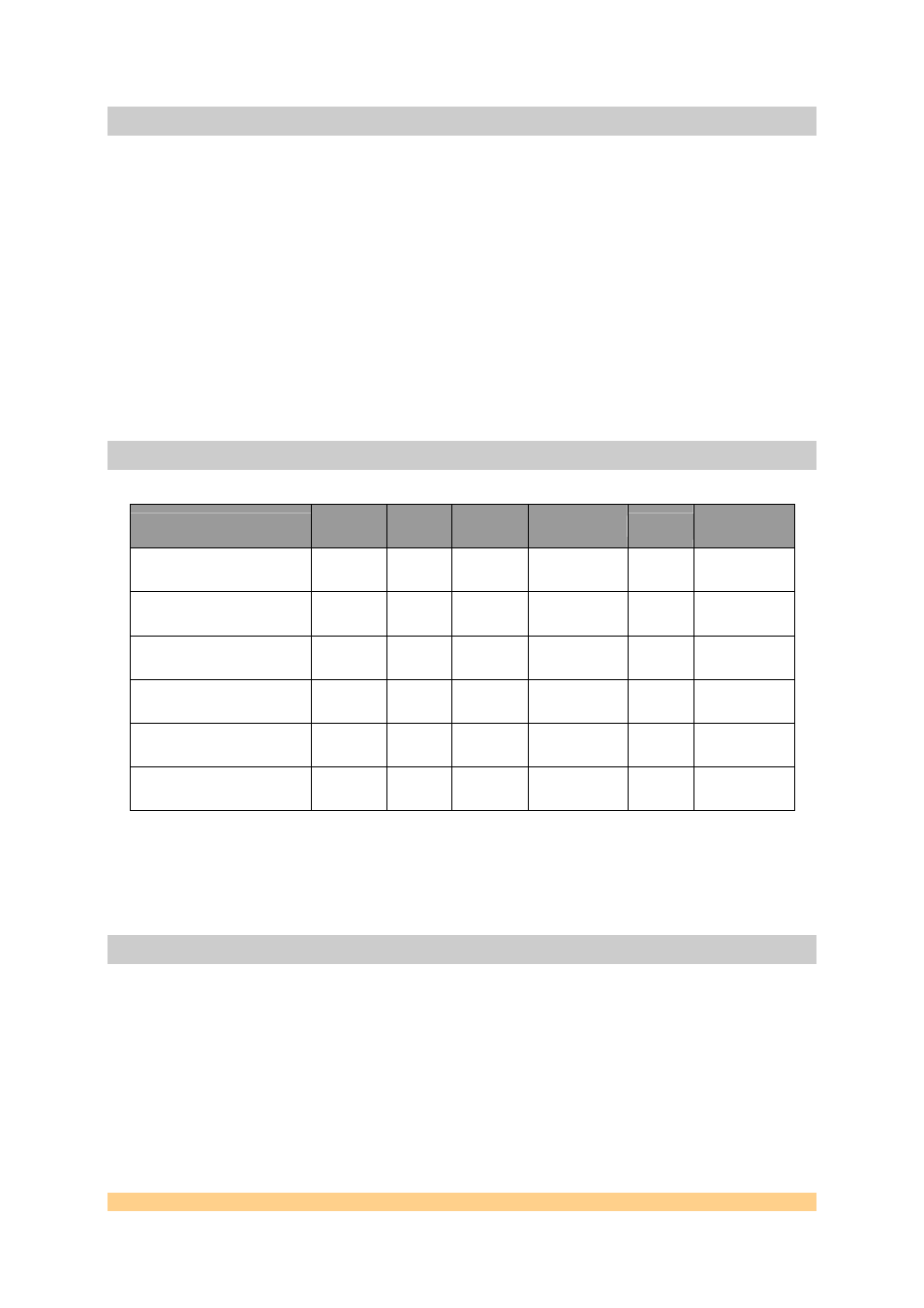

7 Resources usage and performance

FPGA device

FFT

Length

Fmax

(MHz)

Slice

FF

1

Slice LUT

1

BRAM

MULT/

DSP48E

Spartan

®

-3A

XC3SD3400A-5

256 150

23,867 30,143 16

96

SMT348-SX55

XC4VSX55-12

1024 200 21,585 26,079 26

352

SMT351T-SX50

XC5VSX50T-3

1024 250 20,562 20,333 19

176

SMT700-SX95T

XC5VSX95T-2

16,384 200 27,799 29,163 109

256

SMT702-LX110T

XC5VLX110T-3

1,024 250 27,403 33,581 19

32

SMT702-LX110T

XC5VLX110T-3

8,192 250 36,592 44,954 61

44

Notes:

1) Actual slice count dependent on percentage of unrelated logic – see Mapping Report File for details

2) Assuming all core I/Os and clocks are routed off-chip.

8 Testbench and MATLAB program

The core is verified to be bit-accurate with the C/C++ data model under all supported lengths,

modes, throughputs and data format, using a rigorous simulation suite of directed and random

data. Our model development is evaluated in terms of SQNR with a double-precision floating

point software FFT implementation.

User Manual FC100

Page 11 of 12

Last Edited: 25/11/2008 15:00:00