1 clock, 2 nor flash, 1 clock 4.5.2 nor flash – Artesyn SCP-P4040-4G-ENP2 Installation and Use (August 2014) User Manual

Page 33: Table 4-1, Nor flash map, Functional description

Functional Description

SCP-P4040-4G-ENP2 Installation and Use (6806800P60B)

33

4.5.1

Clock

The eLBC clock is generated by platform clock. The divisor is configured by CLKDIV in Clock

Ratio Register (LCRR). The divisor is 32 when GPCM is selected as RCW source. So the eLBC

clock is platform clock / 32 = 800MHz / 32 = 25MHz.

4.5.2

NOR Flash

The NOR FLASH is attached to the GPCM on local bus and works at 16-bit mode.

The NOR FLASH is Numonyx™ PC28F00 BM29EW H. Its size is 2Gb/ 256MB. It has 2048 uniform

blocks, 128K bytes or 64K words each.

The physical address for NOR FLASH is 0xFE0000000 - 0xFEFFFFFFF.

The NOR FLASH should contain RCW data, u-boot image, u-boot environment variables, kernel

image, device tree blob, RAMDISK image and FMAN ucode image. The detailed map is

described in the following table:N

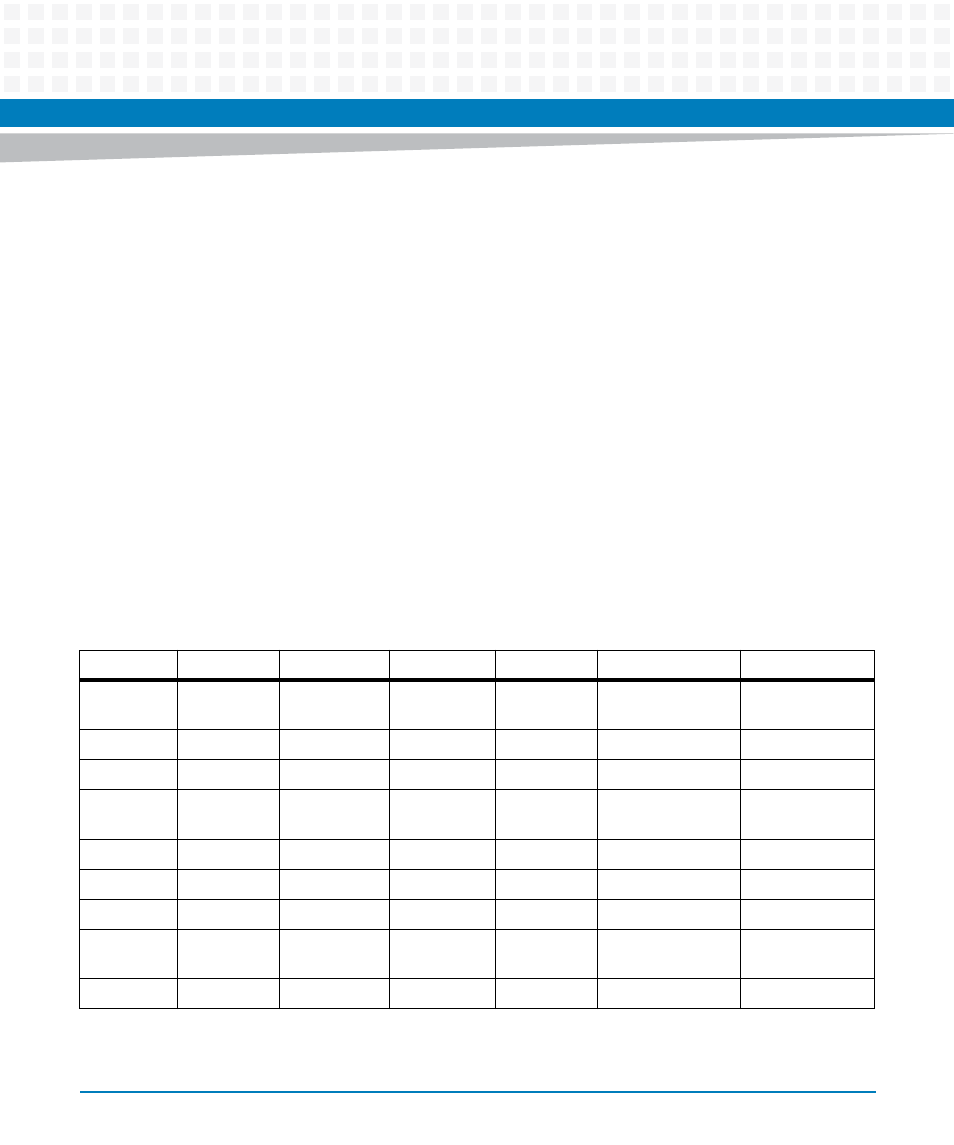

Table 4-1 NOR Flash Map

Block#

Blocks

Start

End

Size

Description

Static/Variable

0

1

0000 0000

0001 FFFF

128 KB

Active RCW

Option Data

Static

1

12

0002 0000

0019 FFFF

1536 KB

RCW Option Data Static

13

3

001A 0000

0020 0000

384KB

Not Used

Static

16

112

0020 0000

00FF FFFF

14 MB

FMAN ucode

Image

Static

128

1792

0100 0000

0EFF FFFF

224 MB

RAMDISK Image

Static

1920

120

0F00 0000

0FEF FFFF

15 MB

Kernel Image

Static

2040

3

0FF0 0000

0FF5 FFFF

384 KB

Device Tree Blob

Static

2043

1

0FF6 0000

0FF7 FFFF

128 KB

U-Boot Env

Variable

Static

2044

4

0FF8 0000

0FFF FFFF

512 KB

U-Boot Image

Static