9 fpga configuration, 9 reset scheme, 10 power management – Artesyn RTM-ATCA-F140 Installation and Use (May 2014) User Manual

Page 51: 9 reset scheme 4.10 power management, Table 4-11, Fpga configuration controls

Functional Description

RTM-ATCA-F140 Installation and Use (6806800M97E)

51

4.8.9

FPGA Configuration

The RTM FPGA configuration is loaded at power-up from one of two SPI Flash devices. One

device is writable/upgradeable and the other is non-writable/golden for recovery purposes.

The selection is which device is used is controlled by switch S1 position 1, according to the

following table.

The configuration Flash devices can be field upgraded using a SPI-controlled Flash programmer

in the FPGA.

4.9

Reset Scheme

The front blade provides a single reset signal, RTM_RST#, over the zone 3 connectors. This

signal is asserted when a master reset of the front blade occurs.

RTM_RST# directly resets the RTM FPGA. The BCM8727, BCM84754, BCM84740, and QSFP+

slot are reset from a secondary reset generated by the RTM FPGA. This allows software control

of the PHY and QSFP+ resets in addition to hardware control via the RTM_RST# signal. After the

hardware reset, the PHYs and QSFP+ are held in reset until released by software.

4.10 Power Management

The front-blade provides two separate power supplies using the Zone 3 connectors:

+3.3 V management power – one pin

+12 V payload power – four pins

The maximum current draw, which is limited by the pin’s current handling capability, is 0.8A for

the management power and 3.2A for the payload power.

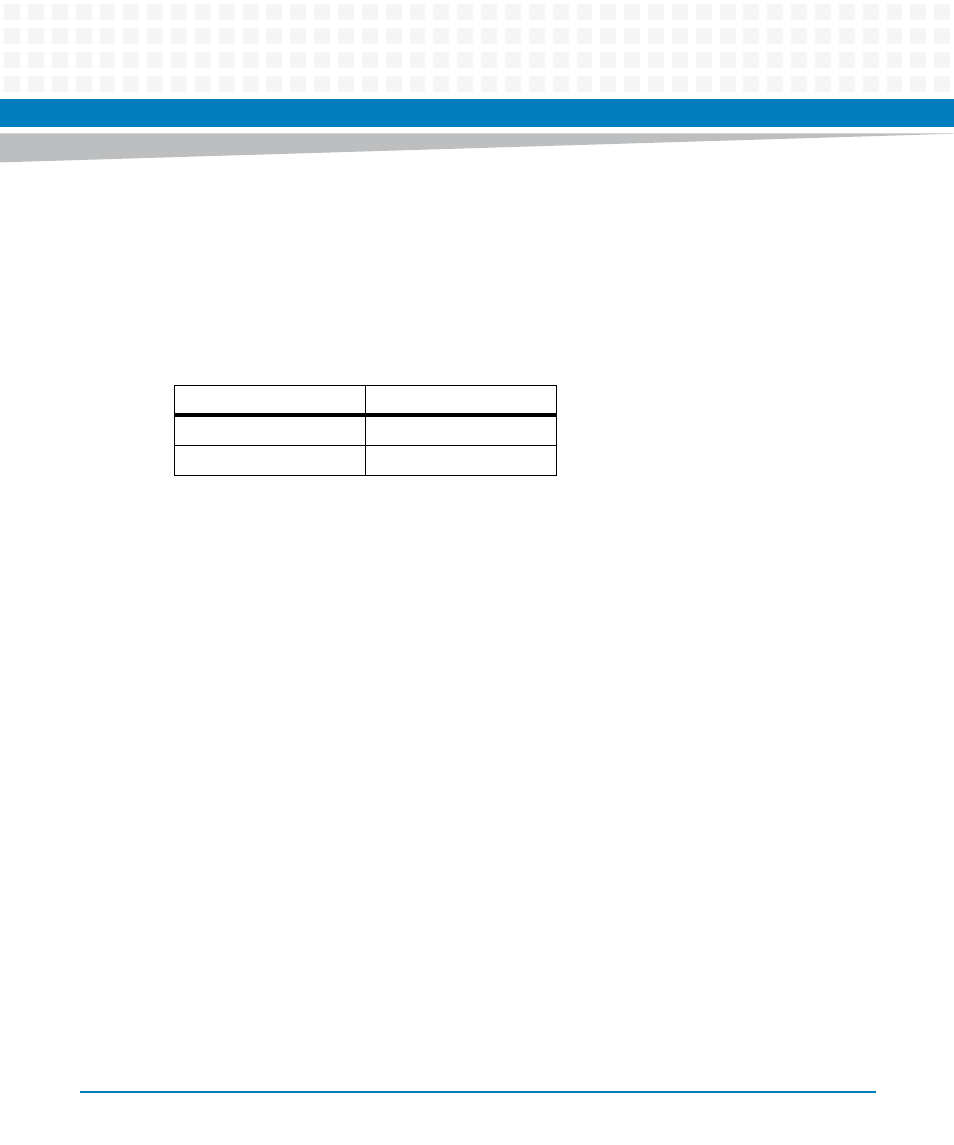

Table 4-11 FPGA Configuration Controls

Switch Setting

FPGA Flash

S1.1 = Off

Writable Bank (default)

S1.1 = On

Non-writable (golden)