System controller, 1 microprocessor, 2 dma controller – Acrosser AR-B1565 User Manual

Page 8

AR-B1565/1565A User!s Guide

7

2. SYSTEM CONTROLLER

This chapter describes the main structure of the AR-B1565/1565A CPU board. The topics are covered as follow:

! Microprocessors

! DMA Controller

! Keyboard Controller

! Interrupt Controller

! Serial Port

! Parallel Port

2.1 MICROPROCESSOR

The AR-B1565/1565A uses the NS GEODE GX1 CPU; it is an advanced 32-bit x86 compatible processor offering

high performance, with fully accelerated 2D graphics, a 64-synchronous DRAM controller and a PCI bus controller,

all on a single chip. This latest generation of the Media GX processor enables a new class of premium

performance notebook/desktop, and IPC computer designs.

The Media GX MMX with enhanced processor companion chips not only provide advanced video and audio

functions but also permit direct interface to memory. This high-performance 64-bit processor is x86 instruction set

compatible and supports MMX technology.

This processor is the latest member of the NS Media GX family, offering high performance; with fully accelerated

2D graphics, synchronous memory interface and a PCI bus controller, all on a single chip. As described in

separate manuals, the CS5520 and the CS5530 I/O Companion chips fully enable the features of the Media GX

processor with MMX support. These features include full VGA and VESA video, 16-bit stereo sound, IDE interface,

ISA interface, SMM power management, and AT compatibility logic. In addition, the newer CS5530 is AC97

Version 2.0 audio compliant that provides an Ultra DMA/33 interface, MPEG2 assist.

In addition to the advanced CPU features, the Media GX processor integrates a host of functions in which typically

implemented with external components. A full-function graphics accelerator provides pixel processing and

rendering functions.

The NS Media GX MMX-Enhanced Processor represents a new generation of x86-compatible 64-bit

microprocessors with sixth-generation features. The decoupled load/store unit (within the memory management

unit) allows multiple instructions in a single clock cycle. Other features include single-cycle execution, single-cycle

instruction decode, 16KB write-back cache, and clock rates up to 300MHz. These features are possible by the use

of advanced-process technologies and super pipelining.

2.2 DMA CONTROLLER

The equivalent of two 8237A DMA controllers are implemented on the AR-B1565/1565A board. Each controller is

a four-channel DMA device that will generate the memory addresses and willcontrol signals necessary to transfer

information directly between a peripheral device and memory. This allows high-speed information transfer with less

CPU intervention. The two DMA controllers are internally cascaded to provide four DMA channels to transfer to 8-

bit peripherals (DMA1) and three channels to transfers to 16-bit peripherals (DMA2). DMA2 channel 0 provides the

cascade interconnection between the two DMA devices, thereby maintaining IBM PC/AT compatibility.

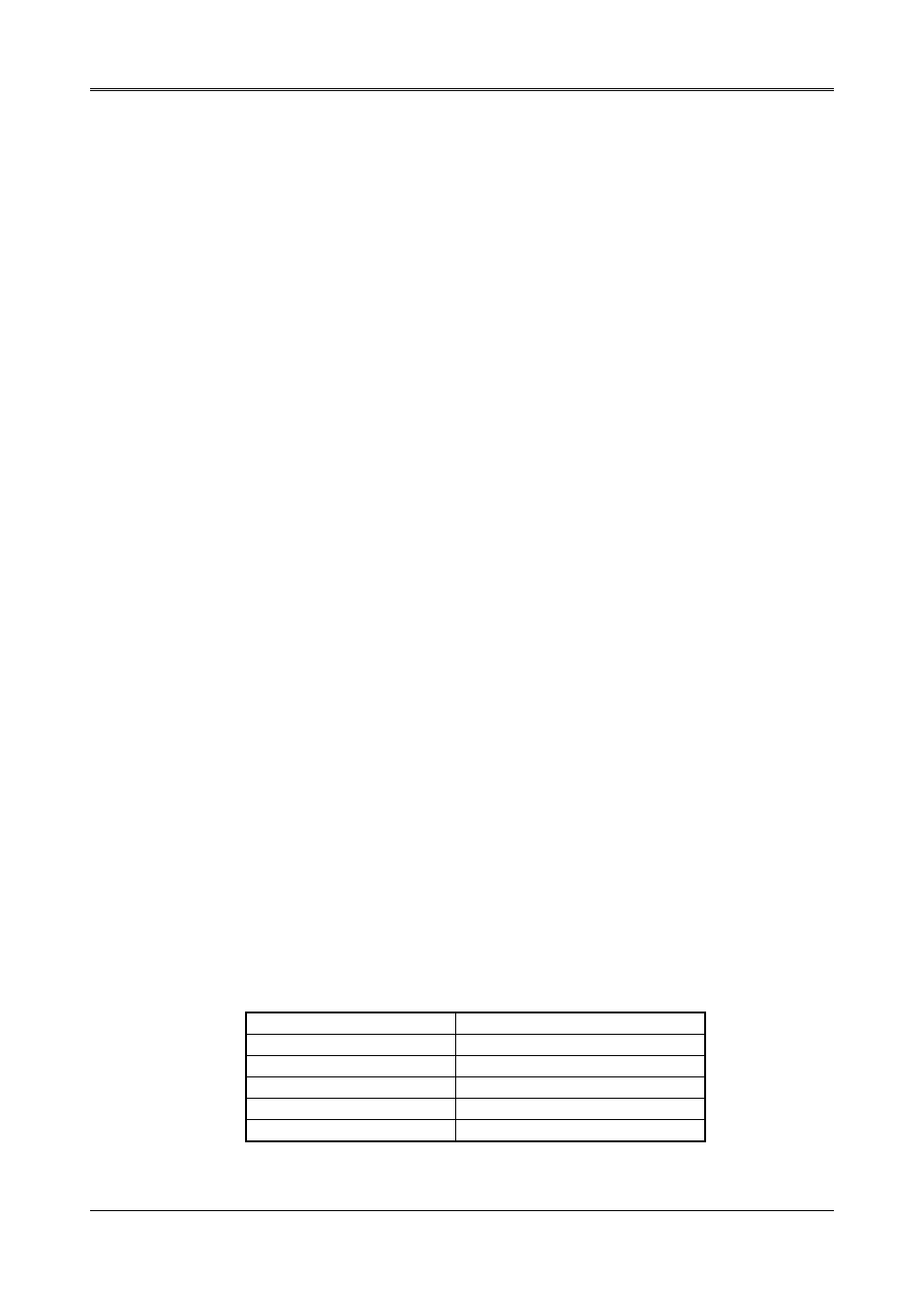

The Following is the system information for the DMA channels:

Slave with four 8-bit channels

Master with three 16-bit channels

DMA Controller 1

DMA Controller 2

Channel 0: Spare

Channel 4(0): Cascade for controller 1

Channel 1: IBM SDLC

Channel 5(1): Spare

Channel 2: Diskette adapter

Channel 6(2): Spare

Channel 3: Spare

Channel 7(3): Spare

DMA Channel Controller