Diamond Power Products MM-48-AT User Manual

Page 19

Diamond-MM-48-AT User Manual V1.01

Page 19

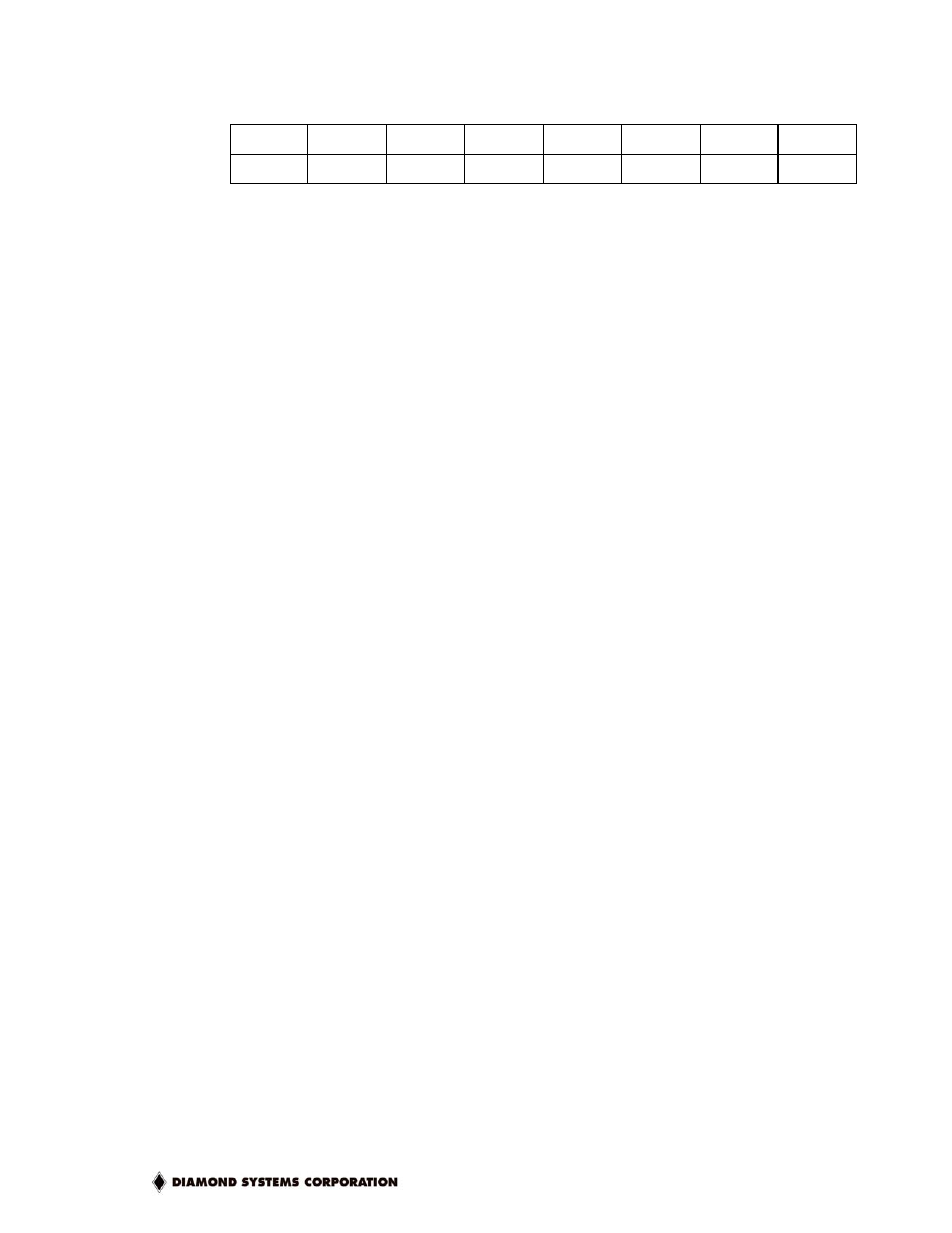

Base + 9

Read

Configuration & Status Register

Bit

No.

7 6 5 4 3 2 1 0

Name ADBUSY DABUSY CKSEL1 CKFRQ1 CKFRQ0

SCNINT CLKEN CLKSEL

ADBUSY A/D chip status:

1 A/D conversion or scan is in progress or A/D input circuit in settling mode

0 A/D is idle

Do not attempt to start a new A/D conversion or scan when ADBUSY = 1.

DABUSY D/A chip status:

1 D/A conversion is in progress

0 D/A is idle

Do not attempt to start a new D/A conversion when DABUSY = 1.

CKSEL1

Clock source select for counter/timer 1:

1 External signal Clk0 in I/O connector J3

0 On-board clock, frequency selected by CKFRQ1 below

CKFRQ1 Clock frequency select for counter/timer 1 when CKSEL1 = 0:

1 100KHz

0 10MHz

CKFRQ0 Clock frequency select for counter/timer 0:

1 1MHz

0 10MHz

SCNINT

Scan interval. This is the time between A/D samples during an A/D scan. An A/D

scan occurs when SCANEN = 1 (Base + 10 bit 4) and an A/D conversion is

triggered.

1 5.0µS

1 9.3µS

CLKEN

Enable hardware A/D clock:

1 Enable hardware A/D trigger (source is selected with CLKSEL bit); software

triggers are disabled

0 Disable hardware trigger; A/D is triggered by setting the ADSTART bit

CLKSEL

A/D clock select, used only when CLKEN = 1:

1 Internal clock: counter/timer 0 generates A/D conversions

0 External clock: the EXTCLK pin on I/O connector J3, generates A/D

conversions