1 alphapc 164sx bcache interface, Figure 4–1 alphapc 164sx l2 bcache array, Alphapc 164sx bcache interface – Compaq 164SX User Manual

Page 42: Alphapc 164sx l2 bcache array, 1 alphapc 164sx bcache interface

4–2

Functional Description

AlphaPC 164SX Bcache Interface

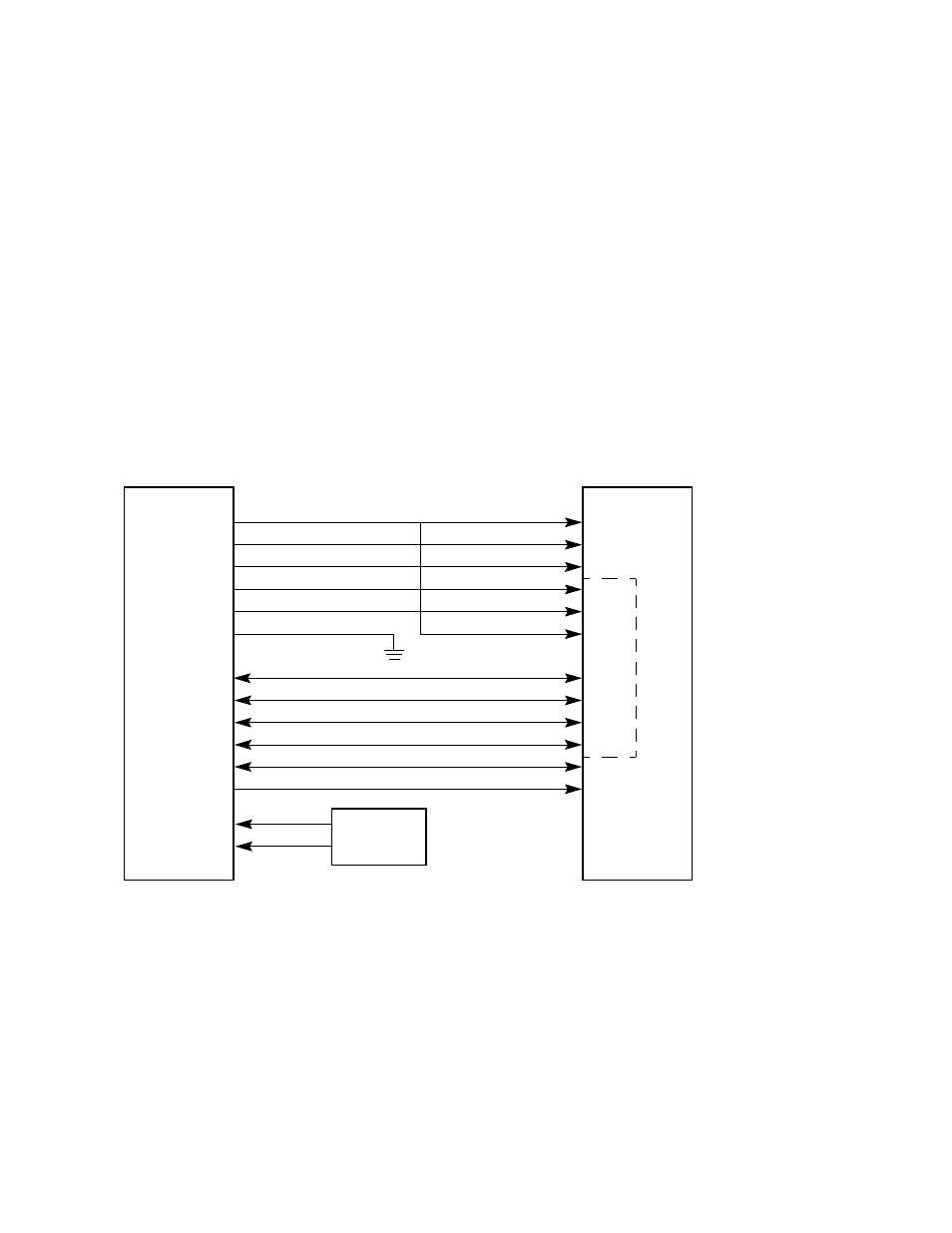

4.1 AlphaPC 164SX Bcache Interface

The 21164PC microprocessor controls the board-level L2 backup cache (Bcache)

array (see Figure 4–1). The data bus (data_h[127:0]) signals are shared with the sys-

tem interface.

Figure 4–1 AlphaPC 164SX L2 Bcache Array

The Bcache is a 1MB, direct-mapped, pipelined, synchronous burst SRAM

(SSRAM) with a 128-bit data path. It is populated with a quantity of four

133-MHz, 64K × 32 SSRAMs for data store, and one 133-MHz, 32K × 32

SSRAM for tag store. The Bcache supports 64-byte transfers to and from

memory.

data_ram_oe_h

21164PC

Microprocessor

Bcache

SRAM

index_h[21:4]

data_ram_we_h

tag_ram_oe_h

tag_ram_we_h

index_h[21:6]

tag_data_h[32:30],19

tag_data_h[29:20]

tag_data_par_h

tag_valid_h

tag_dirty_h

data_h[127:0]

st_clk

x_h

idle_bc_h

fill_dirty_h

Tag

Array

Data

Array

21174