Table 1-1 – Analog Devices SHARC Processors 82-003536-01 User Manual

Page 23

Getting Started With SHARC Processors

1-9

Introduction to SHARC Processors

execution (including single cycle multiply accumulates [MACs]), SHARC

processors are designed for maximum I/O and memory access bandwidth.

This balance of core speed, memory integration, and I/O bandwidth

achieves the sustained performance critical to real-time applications.

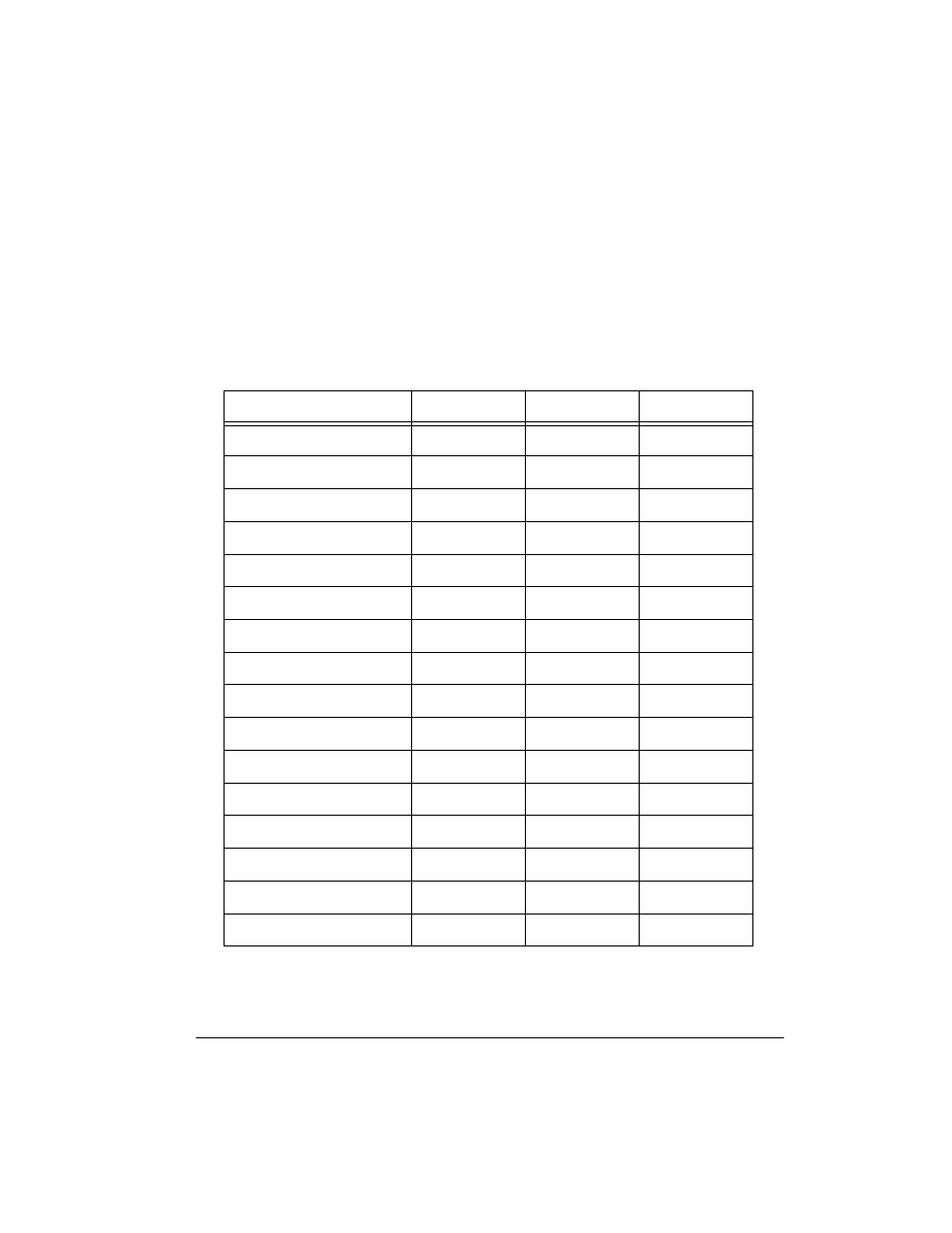

Table 1-1. ADSP-2126x SHARC Processor Specifications

ADSP-21261

ADSP-21262

ADSP-21266

Frequency (MHz)

150

200

200

On-Chip RAM

1M bit

2M bit

2M bit

On-Chip ROM

3M bit

4M bit

4M bit

SRC

0

0

0

PWM

0

0

0

UART

0

0

0

SPI

1

1

1

SPDIF

0

0

0

TWI

0

0

0

Timer

3

3

3

SPORT

4

6

6

SRU

1

1

1

DTCP

0

0

0

PCG

2

2

2

Temp. Grade

–40°C to +85°C

–40°C to +85°C

–40°C to +105°C

Execution from Ext. Memory?

No

No

No