Iii. installation – Asus P/I-XP55T2P4 User Manual

Page 14

8

ASUS P/I-XP55T2P4 User’s Manual

III. INSTALLATION

(Jumpers)

III. INST

ALLA

TION

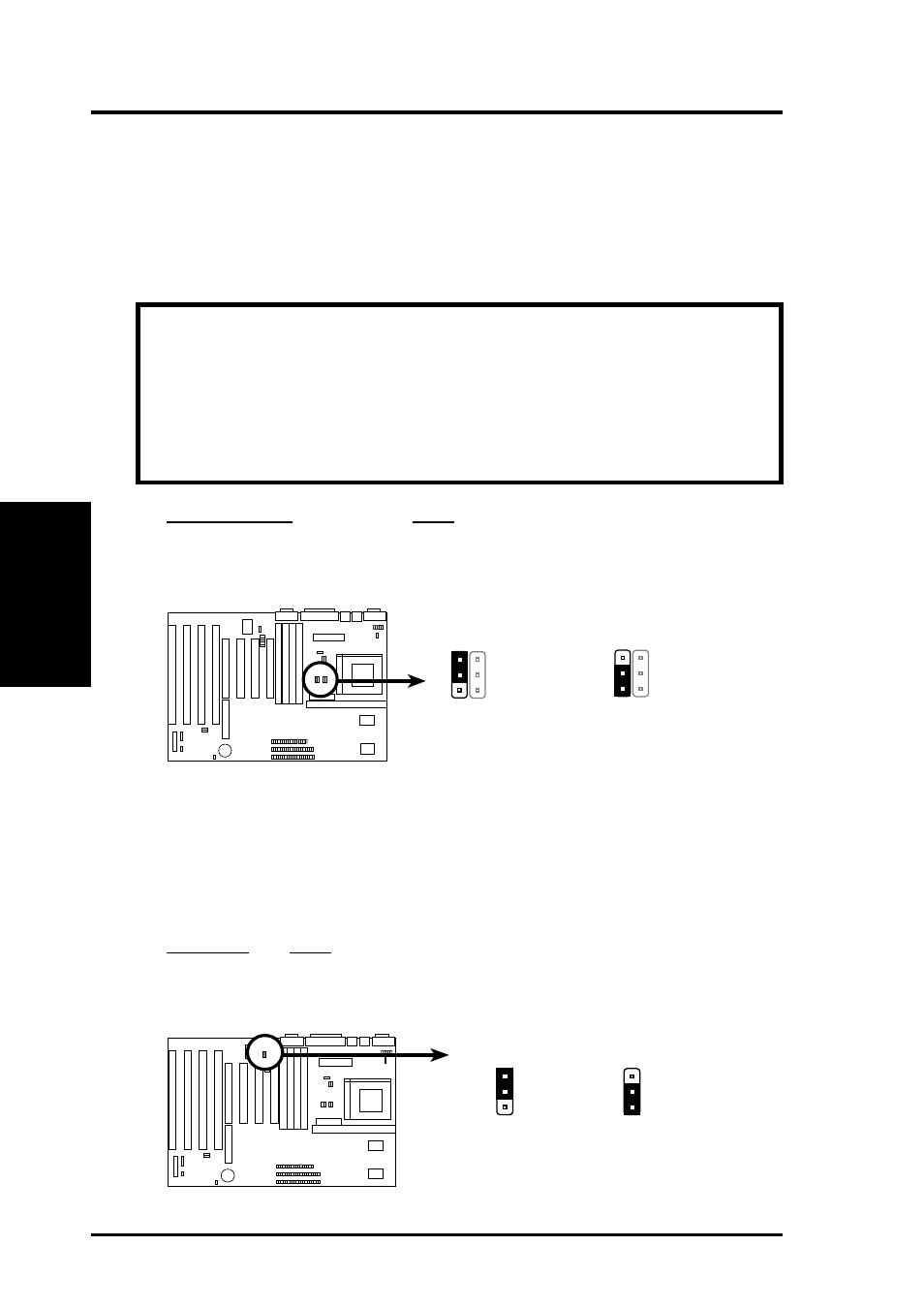

3. Memory Cacheable Size (JP15)

The default of 64MB uses only the onboard TAG SRAM which allows cacheable

memory up to 64MB. If you install DRAM above 64MB and wish to allow

cacheable memory above 64MB, you need to install a TAG SRAM upgrade or

use a cache module with an extended TAG SRAM (such as 256KB ASUS CM1

Rev 3.0 with 2 TAG SRAM's) but not both and set this jumper to 512MB. See

page 12 for TAG SRAM upgrade and page 14 for cache module information.

WARNING: If there are DRAM cache chips (MCache) either onboard or on

the SIMM cache module instead of pipelined burst SRAM chips, this jumper

must be set to 64MB. 512MB will make the system unstable. Mcache chips

can only allow cacheable memory up to 64MB. See "Map of Motherboard" on

page 4 for L2 cache locations. If the cache module that you install already

have an extended tag, do not install another TAG SRAM into the TAG SRAM

Upgrade Socket.

Cacheable Size

JP15

64MB (BSRAM/MCache)

[1-2] (Default)

512MB (BSRAM Only)

[2-3]

Memory Cacheable Size (64MB/512MB)

512MB Cacheable

Burst SRAM Only

JP15

1

2

3

JP15

64MB Cacheable (Default)

Burst SRAM or MCache

1

2

3

4. Onboard Multi-I/O Selection (JP16)

You can selectively disable each onboard Multi-I/O item (floppy, serial, paral-

lel, and IrDA) through BIOS (see pages 35 & 36) or disable all Multi-I/O items

at once with the following jumper in order to use your own Multi-I/O card.

Selections

JP16

Enable

[1-2] (Default)

Disable

[2-3]

Multi I/O Setting (Enable / Disable)

Enable (Default)

Disabled

1

2

3

1

2

3

JP16

JP16