Table 6-2: control register bit assignment – Access PCI-DIO-24D(H) User Manual

Page 16

Manual PCI-DIO-24DH

16

These cards use an 8255-5 PPI to provide a total of 24 bits input/output capability. The card is designed

to use the PPI in Mode 0 wherein:

a.

There are two 8-bit groups (A and B) and two 4-bit groups (C Hi and C Lo).

b.

Any port can be configured as an input or an output.

c.

Outputs are latched.

d.

Inputs are not latched.

The PPI contains a Control Register. This write-only, 8-bit register is used to set the mode and direction of

the ports. At Power-Up or Reset, all I/O lines are set as inputs. The PPI should be configured during

initialization by writing to the Control Registers even if the ports are only going to be used as inputs.

Output buffers are automatically set by hardware according to the Control Register states. Note that

Control Register is located at base address +3 and bit assignments are as follows:

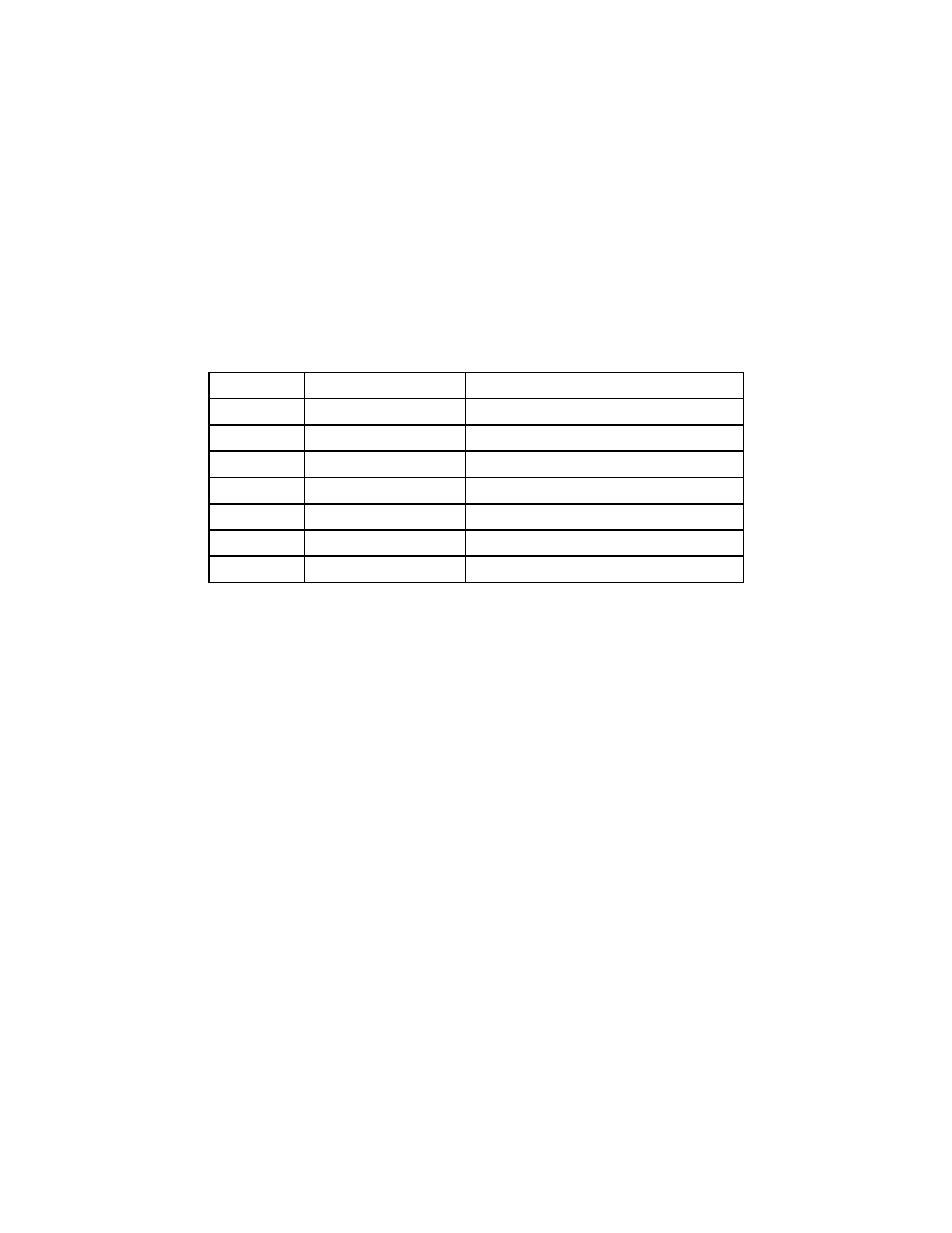

Bit

Assignment

Code

D0

Port C Lo (C0-C3)

1=Input, 0=Output

D1

Port B

1=Input, 0=Output

D2

Mode Select

1=Mode 1, 0=Mode 0

D3

Port C Hi (C4-C7)

1=Input, 0=Output

D4

Port A

1=Input, 0=Output

D5,D6

Mode Select

00=Mode 0, 01=Mode 1, 1X=Mode 2

D7

Mode Set Flag

1=Active

Table 6-2: Control Register Bit Assignment

Note

Mode 1 cannot be used by these cards without modification (Consult factory.). Thus, bits D2, D5, and D6

should always be set to "0". If your card has been modified for use in Mode 1, then there will be an

Addenda sheet in the front of this manual. These cards cannot be used in PPI Mode 2 because of byte &

nibble wide buffering .

Note

In Mode 0, do not use the control register byte for the individual bit control feature. The hardware uses the

I/O bits to control buffer direction on this card. The control register should only be used for setting up input

and output of the ports and enabling the buffer.

These cards provide a means to enable/disable the tristate I/O buffers under program control. If the

TST/BEN jumper on the card is installed in the BEN position, the I/O buffers are permanently enabled.

However, if that jumper is in the TST position, enable/disable of the buffers is software controlled via the

control register as follows:

a.

The card is initialized in the input mode by the computer reset command.

b.

When bit D7 of the Control Register is set high, direction of the three groups of the

associated PPI chip as well as the mode can be set. For example, a write to Base

Address +3 with data bit D7 high programs port direction at 0 ports A, B, and C. If, for

example, hex 80 is sent to Base Address +3, the Port 0 PPI will be configured in mode 0

with Groups A, B, and C as outputs.

At the same time, data bit D7 is also latched in a buffer controller for the associated PPI chip. A high state

disables the buffers and, thus, all four buffers will be put in the tristate mode; i.e. disabled.