AAEON HSB-CV1P User Manual

Page 89

H a l f - s i z e S B C

H S B - C V 1 P

Appendix A Programming the Watchdog Timer A-2

A.1 Programming

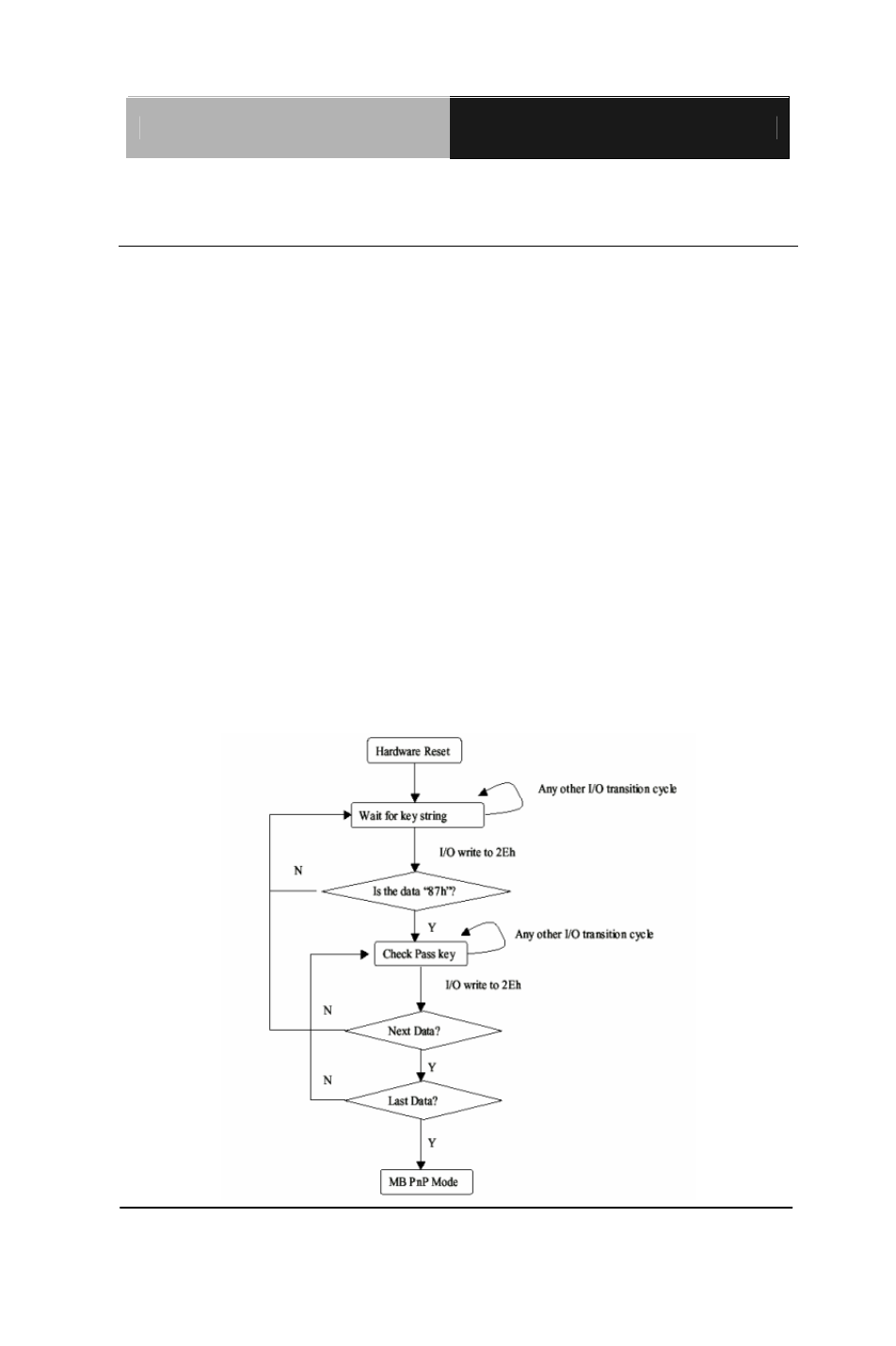

HSB-CV1P utilizes FINTEK 81866 chipset as its watchdog timer

controller. Below are the procedures to complete its configuration

and the AAEON initial watchdog timer program is also

attached based on which you can develop customized

program to fit your application.

Configuring Sequence Description

After the hardware reset or power-on reset, the FINTEK 81866

enters the normal mode with all logical devices disabled

except KBC. The initial state (enable bit ) of this logical device

(KBC) is determined by the state of pin 121 (DTR1#) at the falling

edge of the system reset during power-on reset.

See also other documents in the category AAEON Hardware:

- PCM-QM77 (172 pages)

- PCM-LN02 (70 pages)

- PCM-9452 (64 pages)

- PCM-8120 (71 pages)

- PCM-5895 Rev.A (78 pages)

- PCM-5895 Rev.B (72 pages)

- EPIC-QM77 (138 pages)

- EPIC-CV07 (128 pages)

- EPIC-HD07 (97 pages)

- EPIC-CV01 Series (44 pages)

- EPIC-9456 (59 pages)

- EPIC-9457 Rev.A (62 pages)

- EPIC-9457 Rev.B (58 pages)

- EPIC-5536 (69 pages)

- EPIC-QM57 (79 pages)

- PCM-3116 (1 page)

- PCMCIA_CompactFlash (28 pages)

- PFM-T096P (41 pages)

- PFM-CVS Rev.B (123 pages)

- PCM-3794 Rev.B (1 page)

- PFM-C42C (25 pages)

- PCM-3660 Rev.B (14 pages)

- PFM-C20N (44 pages)

- PFM-P13DW2 (10 pages)

- PFM-535S (53 pages)

- PFM-540I Rev.B (54 pages)

- PFM-540I Rev.А (62 pages)

- PFM-541I (54 pages)

- PFM-HDS (105 pages)

- PFM-CVS Rev.A (107 pages)

- PFM-LNP (44 pages)

- GENE-QM87 (134 pages)

- GENE-5315 (74 pages)

- GENE-HD05 (116 pages)

- GENE-U15B (60 pages)

- GENE-TC05 (109 pages)

- GENE-LN05 Rev.B (64 pages)

- GENE-9455 Rev.B (63 pages)

- GENE-9455 Rev.А (64 pages)

- GENE-9310 (61 pages)

- GENE-QM67 (89 pages)

- GENE-QM57 (75 pages)

- GENE-QM77 Rev.B (157 pages)

- GENE-QM77 Rev.А (101 pages)

- ETX-701 (62 pages)