AAEON EMB-A50M User Manual

Page 40

M i n i - I T X

E M B - A 5 0 M

Appendix A Programming the Watchdog Timer A-4

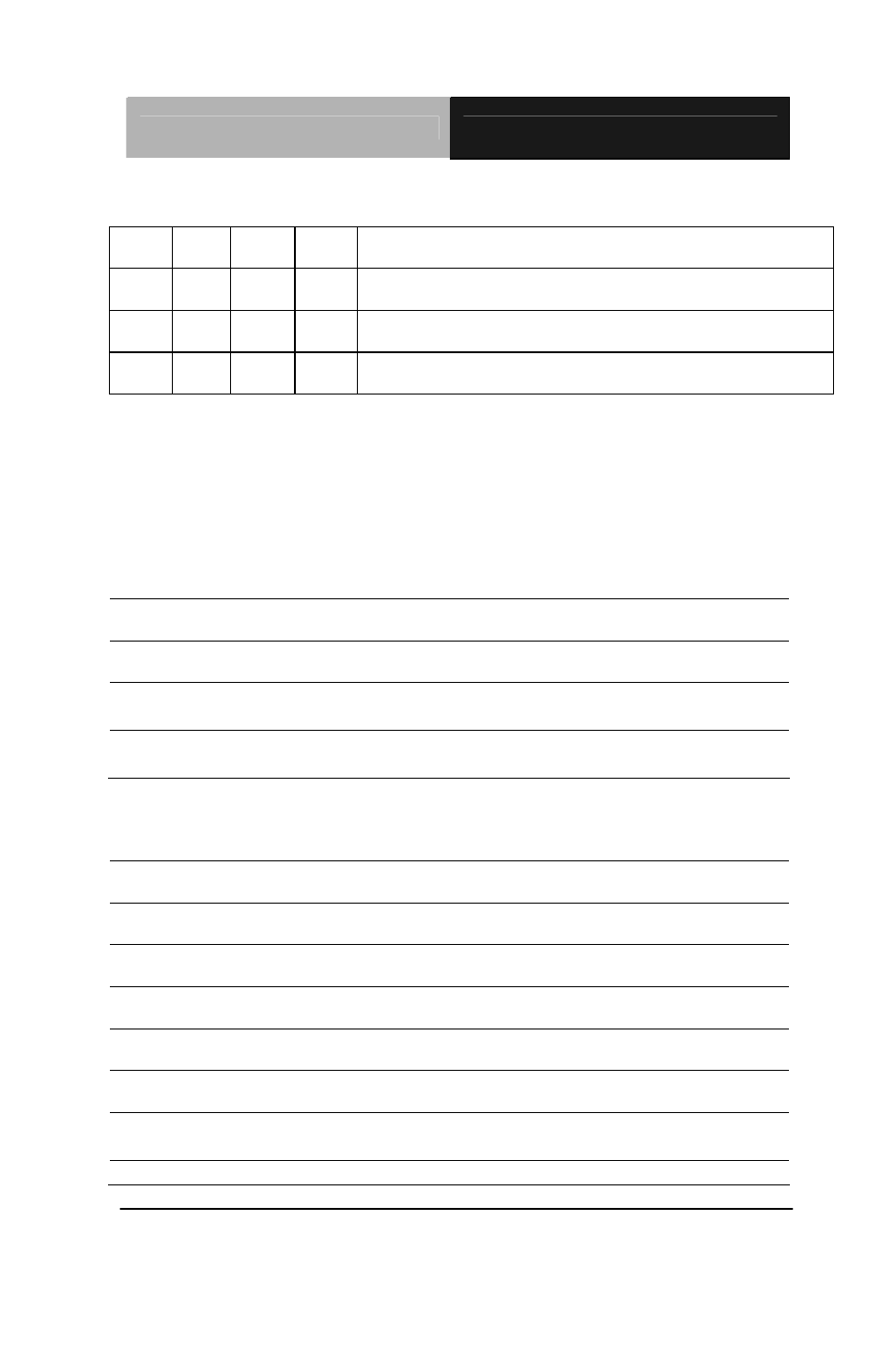

WatchDog Timer Configuration Registers

07h

71h

R/W

00h

Watch Dog Timer Control Register

07h 72h R/W

20h

Watch

Dog

Timer

Configuration Register

07h

73h

R/W

38h

Watch Dog Timer Time-out Value (LSB) Register

07h

74h

R/W

00h

Watch Dog Timer Time-out Value (MSB) Register

Configure Control (Index=02h)

This register is write only. Its values are not sticky; that is to say, a

hardware reset will automatically clear the bits, and does not

require the software to clear them.

Bit Description

7-2 Reserved

1

Returns to the Wait for Key state. This bit is used when the

configuration sequence is completed.

0

Resets all logical devices and restores configuration

registers to their power-on states.

Watch Dog Timer Control Register (Index=71h, Default=00h)

Bit Description

7

WDT is reset upon a CIR interrupt.

6

WDT is reset upon a KBC (Mouse) interrupt.

5

WDT is reset upon a KBC (Keyboard) interrupt.

4 Reserved

3-2 Reserved

1

Force Time-out

This bit is self-cleared.

0 WDT

Status