AAEON PFM-LNP User Manual

Page 36

P C / 1 0 4 C P U M o d u l e

P F M - L N P

Appendix A Programming the Watchdog Timer A-2

A.1 Programming

PFM-LNP utilizes SCH3114-NU chipset as its watchdog timer

controller.

The SCH311X WDT ( Watch Dog Timer ) has a programmable

time-out ranging from 1 to 255 minutes with one minute resolution,

or 1 to 255 second resolution. The unit of the WDT timeout value

are selected via bit[7] of the WDT_TIMEOUT register. The WDT

time-out value is set through the WDT_VAL Runtime register.

Setting The WDT_VAL register to 0x00 disables the WDT function

(this is its power on default).

Setting the WDT_VAL to any other non-zero value will cause the

WDT to reload and begin counting down from the value loaded.

When the WDT count value reaches zero the counter stops and

sets the Watchdog time-out status bit in the WDT_CTRL Runtime

register. Note: Regardless of the current state of the WDT, the WDT

time-out status bit can be directly set or cleared by the Host CPU.

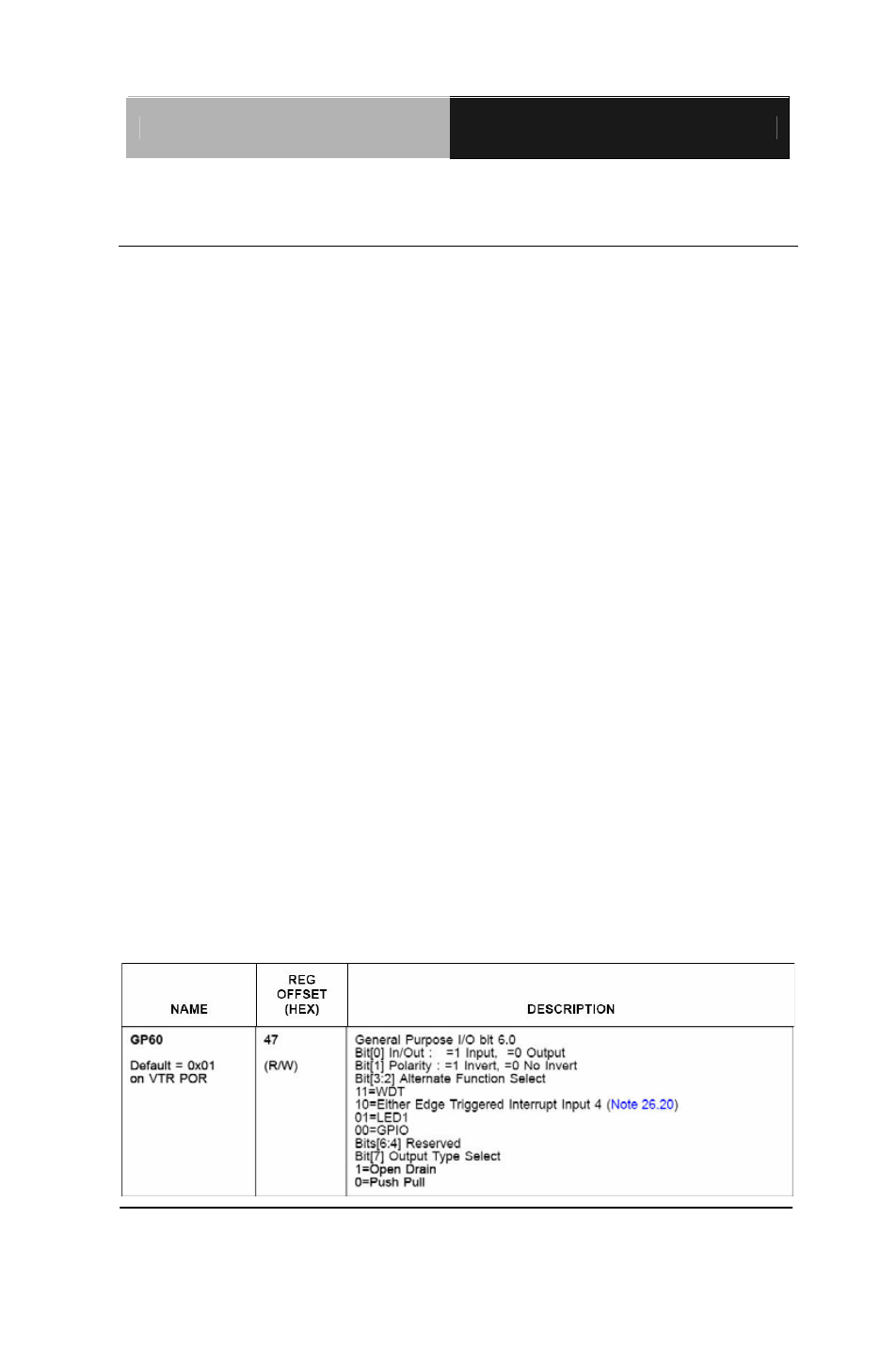

The related register for configuring WDT is list as follows: