D.2 digital i/o register – AAEON EPIC-CV07 User Manual

Page 119

E P I C B o a r d

E P I C - C V 0 7

Appendix D Electrical Specifications for I/O Ports

D-3

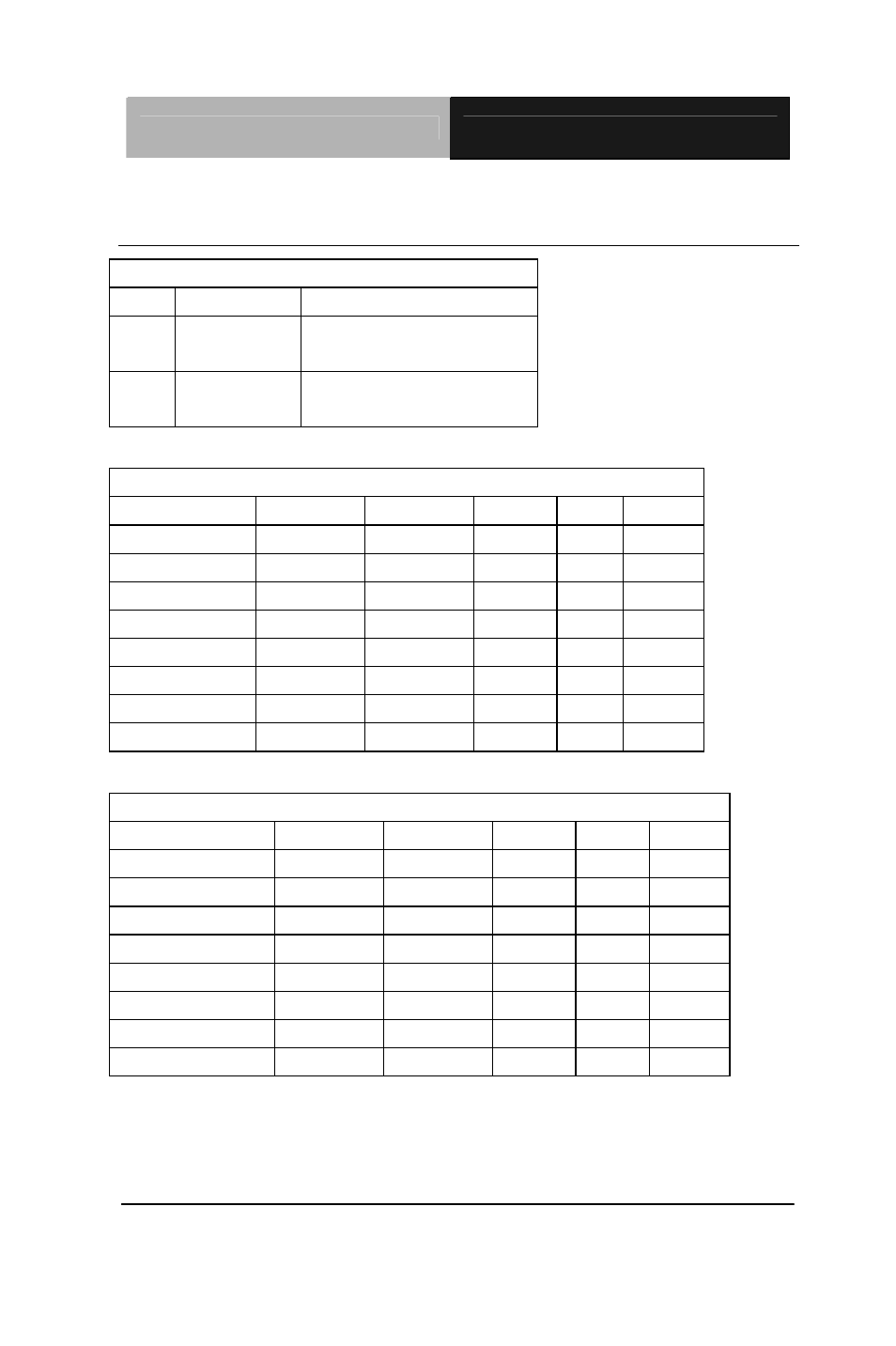

D.2 Digital I/O Register

Table 1 : SuperIO relative register table

Default Value

Note

Index

0x2E

(Note1)

SIO MB PnP Mode Index Register

0x2E or 0x4E

Data

0x2F

(Note2)

SIO MB PnP Mode Data Register

0x2F or 0x4F

Table 2 : Digital Input relative register table

LDN

Register

BitNum

Value

Note

DIO‐0 Pin Status

0x06

(Note3)

0x82

(Note4)

0

(Note5)

GPIO70

DIO‐1 Pin Status

0x06

(Note6)

0x82

(Note7)

1

(Note8)

GPIO71

DIO‐2 Pin Status

0x06

(Note9)

0x82

(Note10)

2

(Note11)

GPIO72

DIO‐3 Pin Status

0x06

(Note12)

0x82

(Note13)

3

(Note14)

GPIO73

DIO‐4 Pin Status

0x06

(Note15)

0x82

(Note16)

4

(Note17)

GPIO74

DIO‐5 Pin Status

0x06

(Note18)

0x82

(Note19)

5

(Note20)

GPIO75

DIO‐6 Pin Status

0x06

(Note21)

0x82

(Note22)

6

(Note23)

GPIO76

DIO‐7 Pin Status

0x06

(Note24)

0x82

(Note25)

7

(Note26)

GPIO77

Table 3 : Digital Output relative register table

LDN

Register

BitNum

Value

Note

DIO‐0 Output Data

0x06

(Note27)

0x81

(Note28)

0

(Note29)

(Note30)

GPIO70

DIO‐1 Output Data

0x06

(Note31)

0x81

(Note32)

1

(Note33)

(Note34)

GPIO71

DIO‐2 Output Data

0x06

(Note35)

0x81

(Note36)

2

(Note37)

(Note38)

GPIO72

DIO‐3 Output Data

0x06

(Note39)

0x81

(Note40)

3

(Note41)

(Note42)

GPIO73

DIO‐4 Output Data

0x06

(Note43)

0x81

(Note44)

4

(Note45)

(Note46)

GPIO74

DIO‐5 Output Data

0x06

(Note47)

0x81

(Note48)

5

(Note49)

(Note50)

GPIO75

DIO‐6 Output Data

0x06

(Note51)

0x81

(Note52)

6

(Note53)

(Note54)

GPIO76

DIO‐7 Output Data

0x06

(Note55)

0x81

(Note56)

7

(Note57)

(Note58)

GPIO77