Rainbow Electronics MAX5351 User Manual

Page 10

MAX535/MAX5351

Low-Power, 13-Bit Voltage-Output DACs

with Serial Interface

10

______________________________________________________________________________________

Shutdown Mode

The MAX535/MAX5351 feature a software-programmable

shutdown that reduces supply current to a typical value

of 4µA. Writing 111XXXXXXXXXXXXX as the input-control

word puts the MAX535/MAX5351 in shutdown mode

(Table 1).

In shutdown mode, the MAX535/MAX5351 output ampli-

fier and the reference input enter a high-impedance

state. The serial interface remains active. Data in the

input registers is retained in shutdown, allowing the

MAX535/MAX5351 to recall the output state prior to

entering shutdown. Exit shutdown mode by either recall-

ing the previous configuration or by updating the DAC

with new data. When powering up the device or bringing

it out of shutdown, allow 20µs for the output to stabilize.

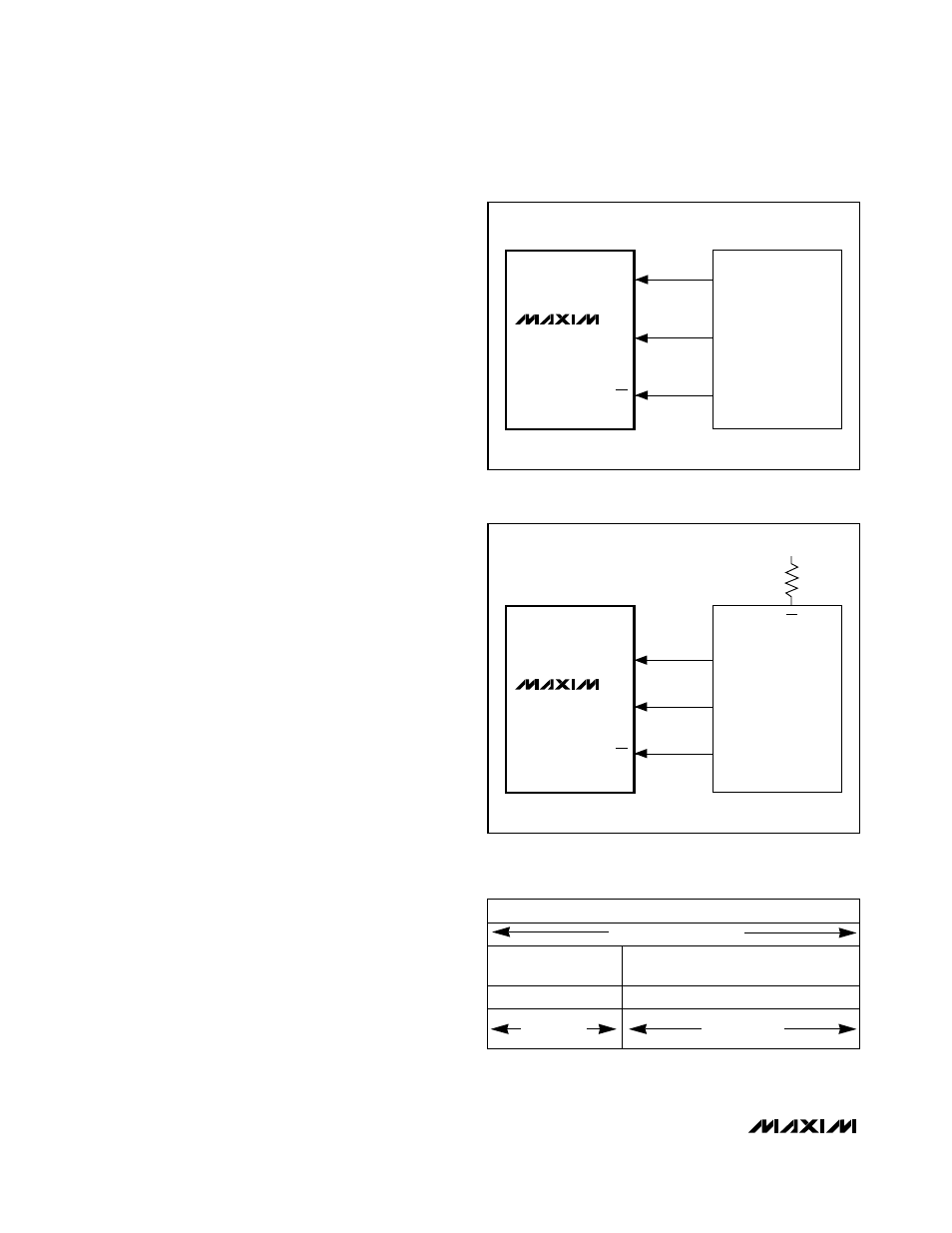

Serial-Interface Configurations

The MAX535/MAX5351’s 3-wire serial interface is com-

patible with both Microwire™ (Figure 2) and

SPI™/QSPI™ (Figure 3). The serial input word consists

of three control bits followed by 13 data bits (MSB first),

as shown in Figure 4. The 3-bit control code determines

the MAX535/MAX5351’s response outlined in Table 1.

The MAX535/MAX5351’s digital inputs are double

buffered. Depending on the command issued through

the serial interface, the input register can be loaded

without affecting the DAC register, the DAC register

can be loaded directly, or the DAC register can be

updated from the input register (Table 1).

Serial-Interface Description

The MAX535/MAX5351 require 16 bits of serial data.

Table 1 lists the serial-interface programming com-

mands. For certain commands, the 13 data bits are

“don’t cares.” Data is sent MSB first and can be sent in

two 8-bit packets or one 16-bit word (

CS must remain

low until 16 bits are transferred). The serial data is com-

posed of three control bits (C2, C1, C0), followed by the

13 data bits D12...D0 (Figure 4). The 3-bit control code

determines:

•

The register to be updated

•

The configuration when exiting shutdown

Figure 5 shows the serial-interface timing requirements.

The chip-select pin (

CS) must be low to enable the DAC’s

serial interface. When

CS is high, the interface control cir-

cuitry is disabled.

CS must go low at least t

CSS

before the

rising serial clock (SCLK) edge to properly clock in the

first bit. When

CS is low, data is clocked into the internal

shift register via the serial-data input pin (DIN) on SCLK’s

rising edge. The maximum guaranteed clock frequency is

10MHz. Data is latched into the MAX535/MAX5351

input/DAC register on

CS’s rising edge.

SCLK

DIN

CS

SK

SO

I/O

MAX535

MAX5351

MICROWIRE

PORT

Figure 2. Connections for Microwire

DIN

SCLK

CS

MOSI

SCK

I/O

SPI/QSPI

PORT

SS

+5V

CPOL = 0, CPHA = 0

MAX535

MAX5351

Figure 3. Connections for SPI/QSPI

Figure 4. Serial-Data Format

3 Control

Bits

13 Data Bits

D12................................................D0

C2

C1

C0

Data Bits

MSB.............................................LSB

Control

Bits

16 Bits of Serial Data

MSB ..................................................................................LSB