Pin descriptions – Rainbow Electronics LM80 User Manual

Page 3

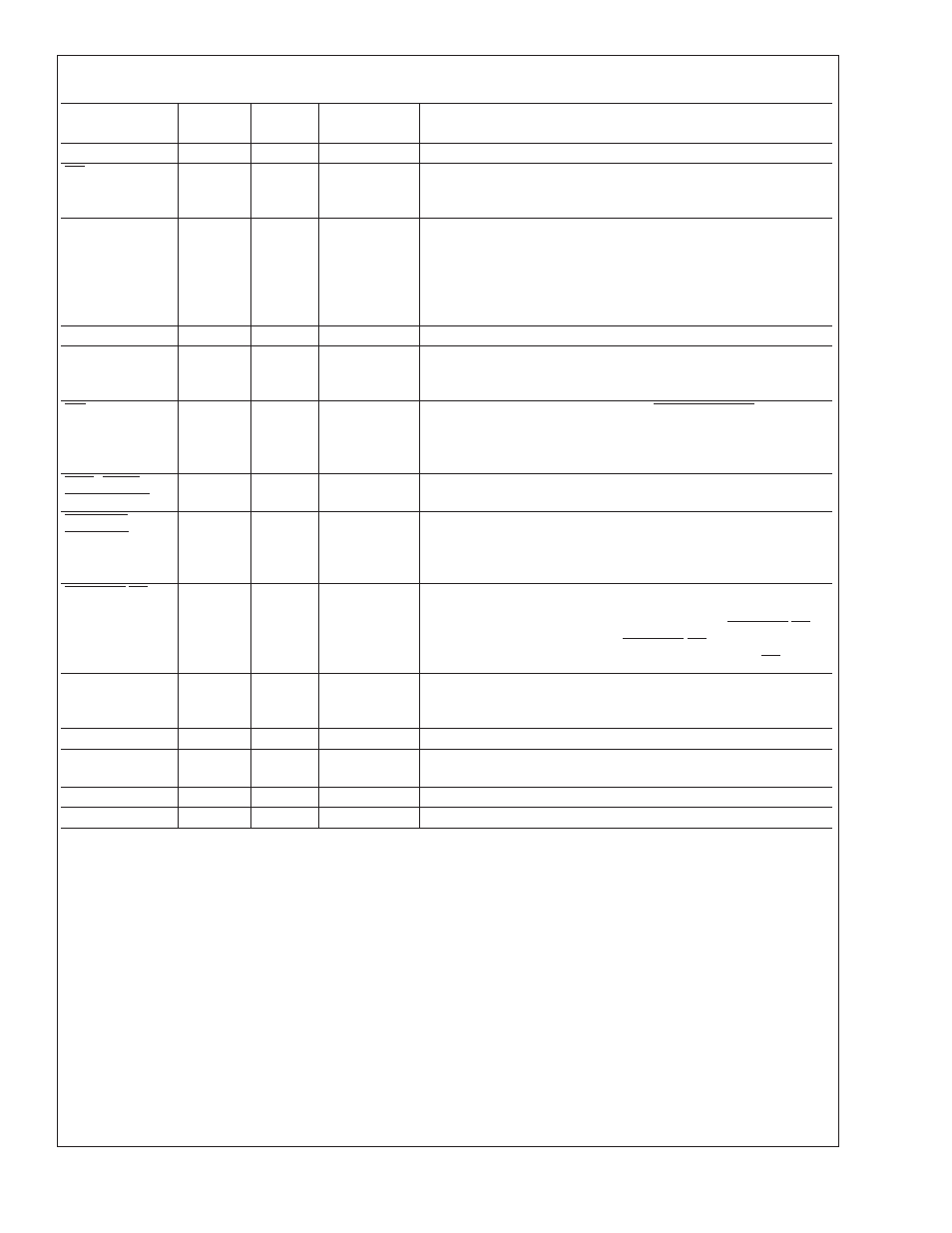

Pin Descriptions

(Continued)

Pin

Name(s)

Pin

Number

Number

of Pins

Type

Description

FAN1-FAN2

4-5

2

Digital Inputs

0 to V

+

fan tachometer inputs.

BTI

6

1

Digital Input

Board Temperature Interrupt driven by O.S. outputs of additional

temperature sensors such as LM75. Provides internal pull-up of

10 k

Ω

.

CI (Chassis

Intrusion)

7

1

Digital I/O

An active high input from an external circuit which latches a Chassis

Intrusion event. This line can go high without any clamping action

regardless of the powered state of the LM80. The LM80 provides an

internal open drain on this line, controlled by Bit 5 of the

Configuration Register, to provide a minimum 10 ms reset of this

line.

GND

8

1

GROUND

Internally connected to all of the digital circuitry.

V

+

(+2.8V to

+5.75V)

9

1

POWER

+3.3V or +5V V

+

power. Bypass with the parallel combination of

10 µF (electrolytic or tantalum) and 0.1 µF (ceramic) bypass

capacitors.

INT

10

1

Digital Output

Non-Maskable Interrupt (open source)/Interrupt Request (open

drain). The mode is selected with Bit 5 of the Configuration Register

and the output is enabled when Bit 1 of the Configuration Register

is set to 1. The default state is disabled.

GPO (Power

Switch Bypass)

11

1

Digital Output

An active low open drain output intended to drive an external

P-channel power MOSFET for software power control.

NTEST_IN/

RESET_IN

12

1

Digital Input

An active-low input that enables NAND Tree board-level connectivity

testing. Refer to Section 10.0 on NAND Tree testing. Whenever

NAND Tree connectivity is enabled the LM80 is also reset to its

power on state.

RST_OUT/OS

13

1

Digital Output

Master Reset, 5 mA driver (open drain), active low output with a

10 ms minimum pulse width. Available when enabled via Bit 4 in

Configuration Register and Bit 7 of the Fan Divisor/RST_OUT/OS

Register. Bit 6 of the Fan Divisor/RST_OUT/OS Register enables

this output as an active low Overtemperature Shutdown (OS).

GNDA

14

1

GROUND

Internally connected to all analog circuitry. The ground reference for

all analog inputs. This pin needs to be taken to a low noise analog

ground plane for optimum performance.

IN6-IN0

15-21

7

Analog Inputs

0V to 2.56V full scale range Analog Inputs.

A0/NTEST_OUT

22

1

Digital I/O

The lowest order bit of the Serial Bus Address. This pin functions as

an output when doing a NAND Tree test.

A1-A2

23-24

2

Digital Inputs

The two highest order bits of the Serial Bus Address.

TOTAL PINS

24

LM80

www.national.com

3