Timing characteristics – Rainbow Electronics MAX117 User Manual

Page 4

MAX113/MAX117

+3V, 400ksps, 4/8-Channel,

8-Bit ADCs with 1µA Power-Down

4

_______________________________________________________________________________________

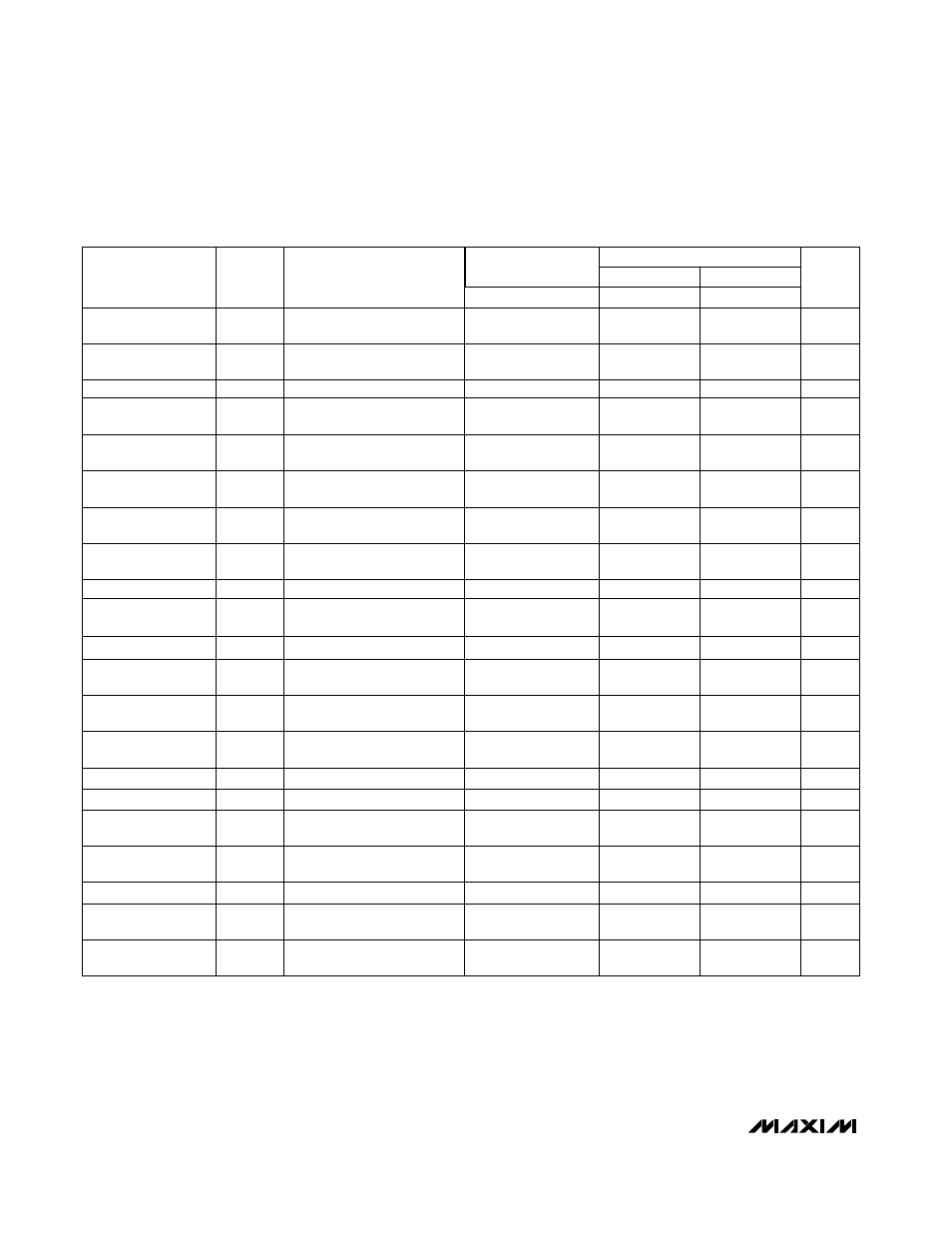

TIMING CHARACTERISTICS

(V

DD

= +3V, T

A

= +25°C, unless otherwise noted.) (Note 4)

Note 4:

Input control signals are specified with t

r

= t

f

= 5ns, 10% to 90% of 3V, and timed from a voltage level of 1.3V. Timing

delays get shorter at higher supply voltages. See the Conversion Time vs. Supply Voltage graph in the

Typical Operating

Characteristics to extrapolate timing delays at other power-supply voltages.

Note 5:

See Figure 1 for load circuit. Parameter defined as the time required for the output to cross 0.66V or 2.0V.

Note 6:

See Figure 2 for load circuit. Parameter defined as the time required for the data lines to change 0.5V.

Note 7:

Also defined as the Minimum Address-Valid to Convert-Start Time.

0.8

10

0.66

10

WR Pulse Width

t

WR

0.6

10

µs

700

Minimum

Acquisition Time

t

ACQ

450

ns

(Note 7)

600

MAX117M

MIN

MAX

MIN

TYP

MAX

PARAMETER

SYMBOL

MIN

MAX

UNITS

CONDITIONS

MAX117C/E

T

A

= +25°C

ALL GRADES

T

A

= T

MIN

to T

MAX

250

Data Access Time

(WR-RD Mode)

t

ACC2

180

ns

t

RD

> t

INTL

, C

L

= 100pF

(Note 5)

220

1.0

600

150

600

400

1.8

70

250

240

Data Access Time

After

INT

t

ID

Delay Between

WR

and

RD Pulses

t

RD

0.8

µs

RD Pulse Width

(WR-RD Mode)

t

READ1

400

ns

100

ns

Multiplexer Address

Hold Time

Data Access Time

(WR-RD Mode)

t

ACC1

400

ns

RD to INT Delay

t

RI

300

ns

WR to INT Delay

t

INTL

0.7

1.45

µs

t

AH

50

ns

Pipelined mode, C

L

= 100pF

RD Pulse Width

(WR-RD Mode)

t

READ2

180

ns

WR to INT Delay

t

IHWR

180

ns

0.9

500

130

t

RD

> t

INTL

, determined by

t

ACC2

t

RD

< t

INTL

, determined by

t

ACC1

500

t

RD

< t

INTL

, C

L

= 100pF

(Note 5)

340

C

L

= 50pF

Pipelined mode, C

L

= 50pF

1.6

60

220

200

150

0

0

140

t

CRD

+

150

180

130

0

0

120

t

CRD

+

130

170

Data Hold Time

t

DH

100

ns

CS to RD, WR

Setup Time

t

CSS

0

ns

CS to RD, WR

Hold Time

t

CSH

0

ns

CS to RDY Delay

t

RDY

100

ns

(Note 6)

Data Access Time

(RD Mode)

t

ACC0

t

CRD

+

100

ns

RD to INT Delay

(RD Mode)

t

INTH

100

160

ns

C

L

= 100pF (Note 5)

C

L

= 50pF,

R

L

= 5.1k

Ω

to V

DD

C

L

= 50pF

2.4

2.06

Conversion Time

(WR-RD Mode)

t

CWR

1.8

µs

t

RD

< t

INTL

, C

L

= 100pF

(Note 5)

1.4

1.2

Power-Up Time

t

UP

0.9

µs

2.6

2.4

Conversion Time

(RD Mode)

t

CRD

2.0

µs