Rainbow Electronics DS1993 User Manual

Page 9

DS1992/DS1993/DS1994

9 of 23

102199

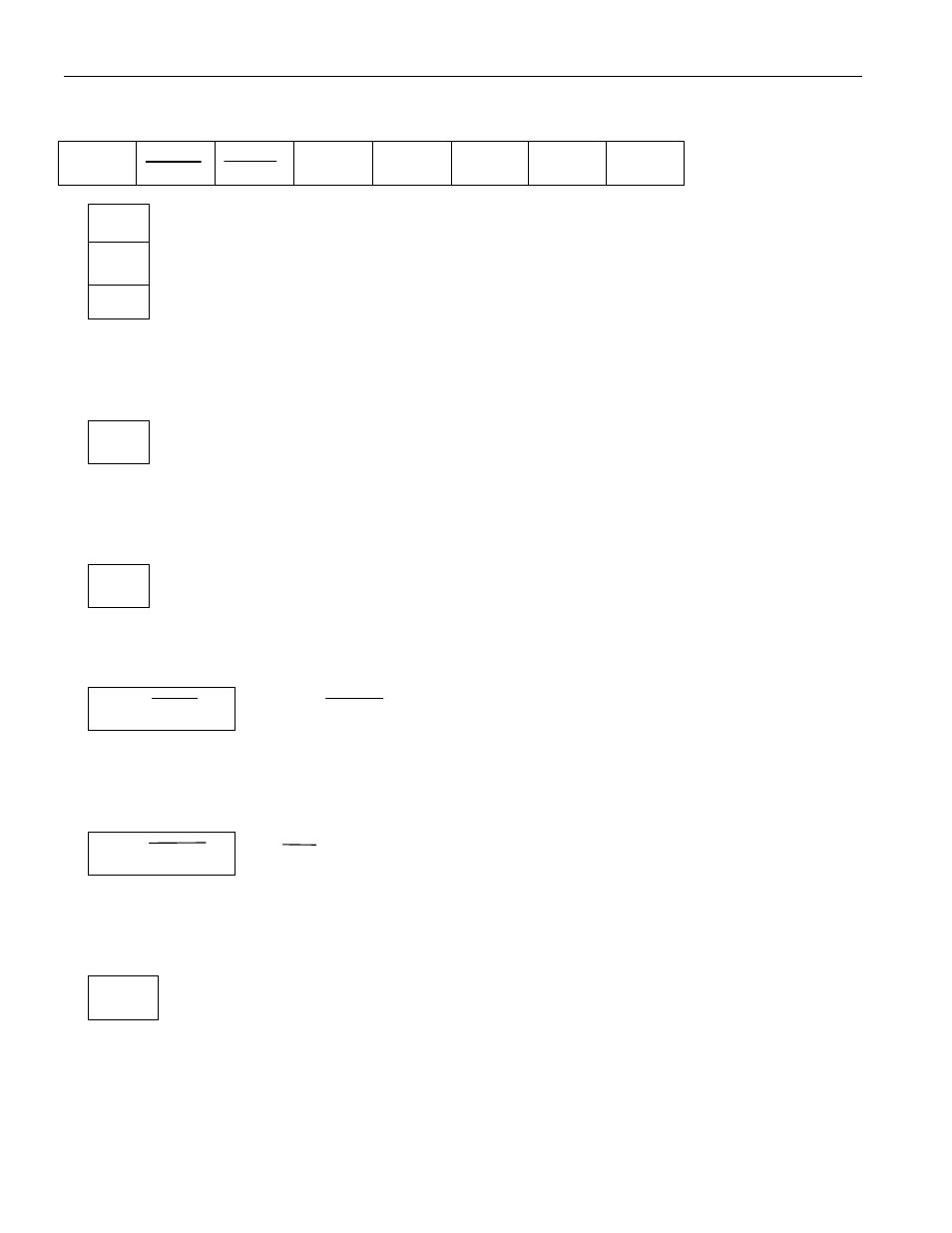

Control Register

7

6

5

4

3

2

1

0

DSEL

STOP

START

AUTO

MAN.

OSC

RO

WPC

WPI

WPR

0201h

0

WPR

Write protect real-time clock/alarms registers

1

WPI

Write protect interval timer/alarms registers

2

WPC

Write protect cycle counter/alarms registers

Setting a write protect bit to a logic 1 will permanently write protect the corresponding counter and alarm

registers, all write protect bits, and additional bits in the control register. The write protect bits can not be

written in a normal manner (see “Write Protect/Programmable Expiration” section).

3

RO

Read only

If a programmable expiration occurs and the read only bit is set to a logic 1, then the DS1994 becomes

read only. If a programmable expiration occurs and the read only bit is a logic 0, then only the 64-bit

lasered ROM can be accessed (see “Write Protect/Programmable Expiration” section).

4

OSC

Oscillator enable

This bit controls the crystal oscillator. When set to a logic 1, the oscillator will start operation. When the

oscillator bit is a logic 0, the oscillator will stop.

5

AUTO/MAN

Automatic/Manual Mode

When this bit is set to a logic 1, the interval timer is in automatic mode. In this mode, the interval timer is

enabled by the data line. When this bit is set to a logic 0, the interval timer is in manual mode. In this

mode the interval timer is enabled by the STOP/START bit.

6

STOP/START

Stop/Start (in Manual Mode)

If the interval timer is in manual mode, the interval timer will start counting when this bit is set to a logic

0 and will stop counting when set to a logic 1. If the interval timer is in automatic mode, this bit has no

effect.

7

DSEL

Delay Select Bit

This bit selects the delay that it takes for the cycle counter and the interval timer (in auto mode) to see a

transition on the data line. When this bit is set to a logic 1, the delay time is 123

±

2 ms. This delay allows

communication on the data line without starting or stopping the interval timer and without incrementing

the cycle counter. When this bit is set to a logic 0, the delay time is 3.5

±

0.5 ms.