Table 1. timer pin modes – Rainbow Electronics DS4560 User Manual

Page 6

DS4560

12V Hot-Plug Switch

6

_______________________________________________________________________________________

Enable/Timer

The voltage level of the TIMER pin is compared to an

internal source (see the

Block Diagram)

. When the level

on the pin exceeds V

ON

, the comparator outputs a low

level. This then turns on the voltage ramp circuit,

enabling the device’s output. This TIMER pin can be

configured into one of four different modes of operation

listed in Table 1. The TIMER pin was designed to work

with most logic families. The TIMER pin will have at

least 250mV of hysteresis between V

ON

and V

OFF

. It is

recommended that any logic gate used to drive the

TIMER pin be tested to ensure proper operation.

Once the device has been enabled, there is a delay

(t

POND

) until conduction begins from V

CC

to LOAD.

This delay is the time required for the charge pump to

bring the gate voltage of the power MOSFET above its

threshold level. Once the gate is above the threshold

level, conduction begins and the output voltage begins

ramping.

Automatic Enable Mode

When V

CC

exceeds V

UVLOR

, the gate holding the

TIMER node low is released. The internal current

source brings the node to a level greater than V

ON

,

enabling the device.

Delayed Automatic Enable Mode

When V

CC

exceeds V

UVLOR

, the gate holding the

TIMER node low is released. The internal current

source (I

TIMER

) then begins charging C

TIMER

. When

C

TIMER

is charged to a level greater than V

ON

, the

device turns on. The equation for the delay time is:

t

DELAY

= (C

TIMER

x V

ON

)/I

TIMER

Enable/Disable Mode

A logic gate or open-collector device can be connect-

ed to the TIMER pin to enable or disable the device.

When the TIMER pin is held low, the device is disabled.

When an open-collector device is used to drive the

TIMER pin, the DS4560 is enabled when the open col-

lector is in its high-impedance state by the internal cur-

rent source bringing the TIMER node high. The TIMER

pin is also compatible with most logic families if the out-

put high voltage level of the gate exceeds the V

ON

level, and the gate can sink the I

TIMER

current.

Enable with Delay/Disable Mode

An open-collector device is connected in parallel with

C

TIMER

. When the pin is held low, the DS4560 is dis-

abled. When the open-collector driver is high imped-

ance, the internal current source begins to charge

C

TIMER

as in the delayed mode.

Output-Voltage Ramp

The voltage ramp circuit uses an operational amplifier

to control the gate bias of the n-channel power

MOSFET. When the timer/enable circuit is disabled, a

FET is used to keep C

VRAMP

discharged, which forces

the output voltage to GND. Once the enable/timer cir-

cuit has been enabled, an internal current source,

I

VRAMP

, begins to charge the external capacitor,

C

VRAMP

, connected to the VRAMP pin. The amplifier

controls the gate of the power MOSFET so that the

LOAD output voltage divided by two tracks the rising

voltage level of C

VRAMP

. The output voltage continues

to ramp until it reaches either the input V

CC

level or the

overvoltage clamp limits. The equation for the output-

voltage ramp function is:

dV

LOAD

/dt = 2 x (I

VRAMP

/C

VRAMP

)

Thermal Shutdown

The DS4560 enters a thermal shutdown state when the

temperature of the power MOSFET reaches or exceeds

T

SHDN

, approximately +135°C. When T

SHDN

is exceed-

ed, the thermal-limiting circuitry disables the DS4560

using the enable circuitry. The DS4560 is offered in two

different versions: an autoretry version and a latchoff

version.

Autoretry Version (DS4560S-AR)

The autoretry verson continually monitors the tempera-

ture once it has entered thermal shutdown. If the junc-

tion temperature falls below approximately +95°C

(T

SHDN

- T

HYS

), the power MOSFET is re-enabled. See

the THERMAL SHUTDOWN WITH AUTORETRY graph

for details.

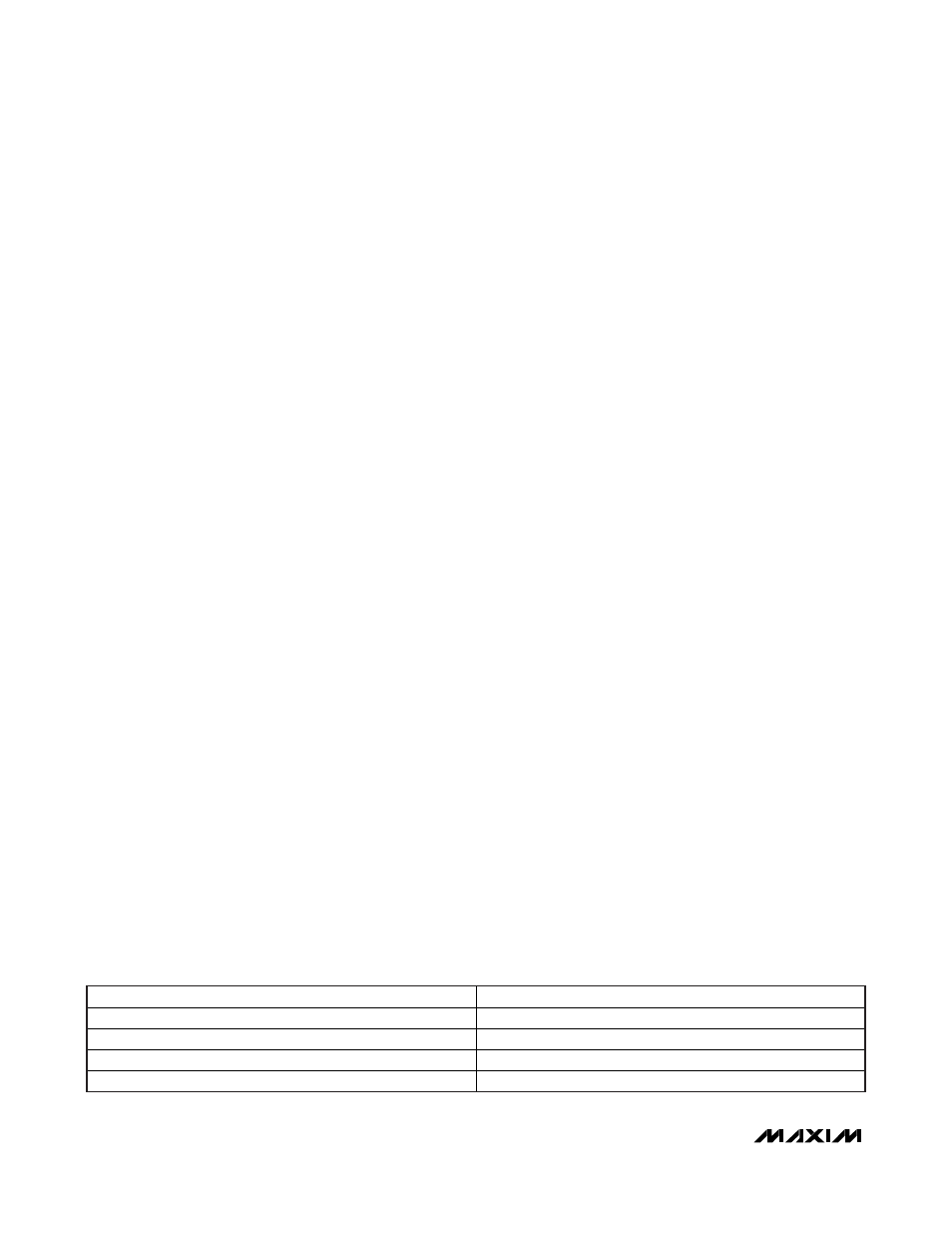

Table 1. TIMER Pin Modes

MODE OF OPERATION

TIMER PIN SETUP

Automatic Enable

No connection to TIMER pin.

Delayed Automatic Enable

Capacitor C

TIMER

connected to TIMER.

Enable/Disable Open-collector

device.

Enable with Delay/Disable

Open-collector device and C

TIMER

.