Dynamic characteristics – Rainbow Electronics ADC08832 User Manual

Page 5

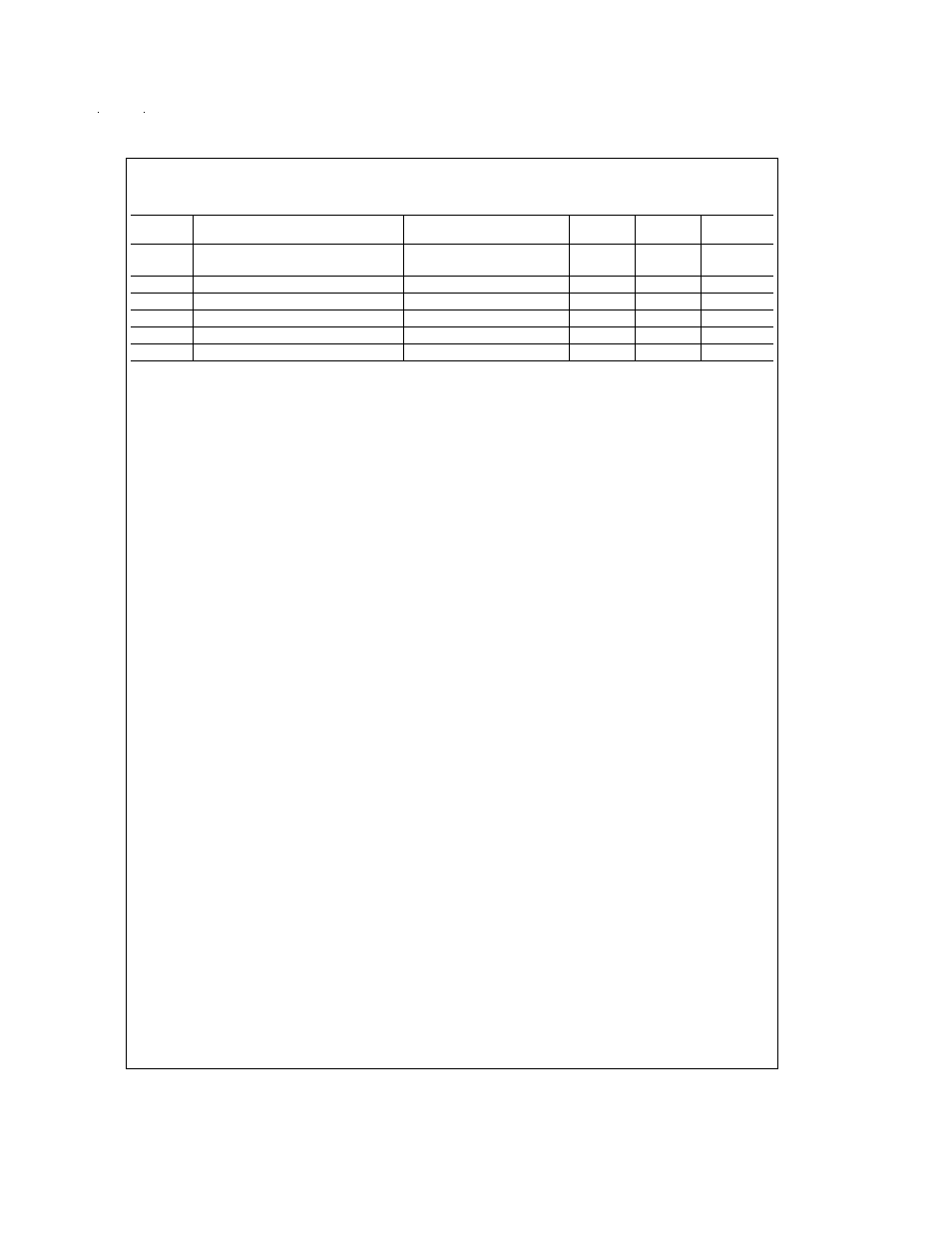

Dynamic Characteristics

The following specifications apply for V

CC

= 5V, f

CLK

= 2MHz, T

A

= 25˚C, R

SOURCE

= 50

Ω

, f

IN

= 45kHz, V

IN

= 5V

P-P

, V

REF

=

5V, non-coherent 2048 samples with windowing.

Symbol

Parameter

Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

f

S

Sampling Rate

ADC08831

ADC08832

f

CLK

/11

f

CLK

/13

181

153

ksps

ksps

SNR

Signal-to -Noise Ratio (Note 19)

48.5

dB

THD

Total Harmonic Distortion (Note 20)

−59.5

dB

SINAD

Signal-to -Noise and Distortion

48.0

dB

ENOB

Effective Number Of Bits (Note 18)

7.7

Bits

SFDR

Spurious Free Dynamic Range

62.5

dB

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional. These ratings do not guarantee specific performance limits. For guaranteed speci-

fications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance character-

istics may degrade when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to GND = 0 V

DC

, unless otherwise specified.

Note 4: When the input voltage V

IN

at any pin exceeds the power supplies (V

IN

<

(GND) or V

IN

>

V

CC

,) the current at that pin should be limited to 5 mA. The 20

mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four pins.

Note 5: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

JMAX

,

θ

JA

and the ambient temperature, T

A

. The maximum

allowable power dissipation at any temperature is P

D

= (T

JMAX

− T

A

)/

θ

JA

or the number given in the Absolute Maximum Ratings, whichever is lower.

Note 6: Human body model, 100 pF capacitor discharged through a 1.5 k

Ω

resistor. The machine mode is a 200pF capacitor discharged directly into each pin.

Note 7: See AN450 “Surface Mounting Methods and Their Effect on Product Reliability” or Linear Data Book section “Surface Mount” for other methods of soldering

surface mount devices.

Note 8: Typicals are at T

J

= 25˚C and represent the most likely parametric norm.

Note 9: Guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 10: Total unadjusted error includes offset, full-scale, linearity, multiplexer errors.

Note 11: It is not tested for the ADC08832.

Note 12: For V

IN(−)

≥

V

IN(+)

the digital code will be 0000 0000. Two on-chip diodes are tied to each analog input (see Functional Block Diagram) which will

forward-conduct for analog input voltages one diode drop below ground or one diode drop greater than V

CC

supply. During testing at low V

CC

levels (e.g., 4.5V), high

level analog inputs (e.g., 5V) can cause an input diode to conduct, especially at elevated temperatures, which will cause errors for analog inputs near full-scale. The

spec allows 50 mV forward bias of either diode; this means that as long as the analog V

IN

does not exceed the supply voltage by more than 50 mV, the output code

will be correct. Exceeding this range on an unselected channel will corrupt the reading of a selected channel. Achievement of an absolute 0 V

DC

to 5 V

DC

input voltage

range will therefore require a minimum supply voltage of 4.950 V

DC

over temperature variations, initial tolerance and loading.

Note 13: Channel leakage current is measured after a single-ended channel is selected and the clock is turned off. For off channel leakage current the following two

cases are considered: one, with the selected channel tied high (5 V

DC

) and the remaining off channel tied low (0 V

DC

), total current flow through the off channel is

measured; two, with the selected channel tied low and the off channels tied high, total current flow through the off channel is again measured. The two cases con-

sidered for determining on channel leakage current are the same except total current flow through the selected channel is measured.

Note 14: A 40% to 60% duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of these limits

the minimum time the clock is high or low must be at least 250 ns. The maximum time the clock can be high or low is 60 µs.

Note 15: Since data, MSB first, is the output of the comparator used in the successive approximation loop, an additional delay is built in to allow for comparator re-

sponse time.

Note 16: For the ADC08832 V

ref

is internally tied to V

CC

, therefore, for the ADC08832 reference current is included in the supply current.

Note 17: Analog inputs are typically 300 ohms input resistance to a 13pF sample and hold.

Note 18: Effective Number Of Bits (ENOB) is calculated from the measured signal-to-noise plus distortion ratio (SINAD) using the equation ENOB = (SINAD-1.76)/

6.02.

Note 19: The signal-to-noise ratio is the ratio of the signal amplitude to the background noise level. Harmonics of the input signal are not included in it’s calculation.

Note 20: The contributions from the first 6 harmonics are used in the calculation of the THD.

www.national.com

5