Electrical characteristics – Rainbow Electronics ADC08832 User Manual

Page 4

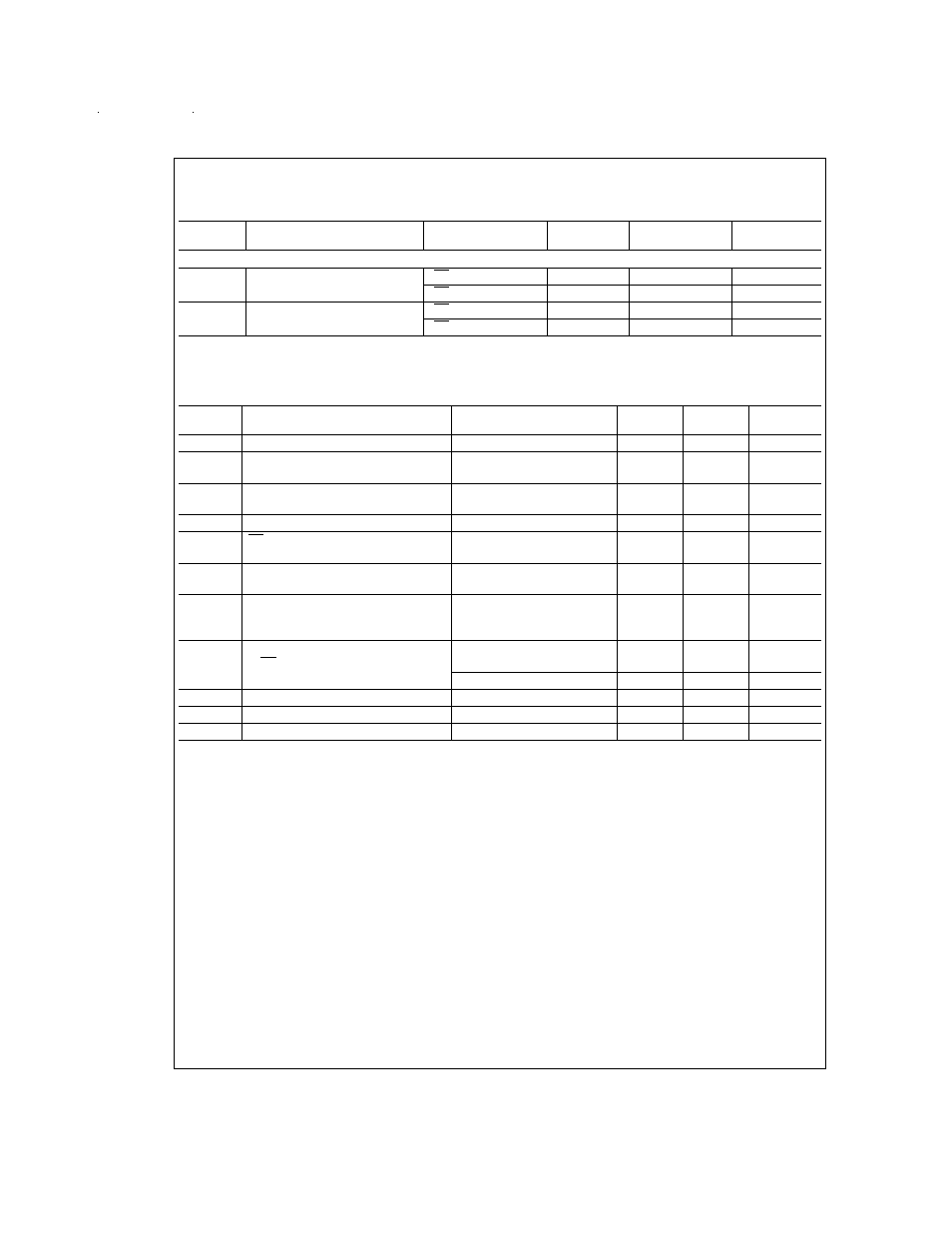

Electrical Characteristics

(Continued)

The following specifications apply for V

CC

= V

REF

= +5V

DC

, and f

CLK

= 2 MHz unless otherwise specified. Boldface limits

apply for T

A

= T

J

= T

MIN

to T

MAX

; all other limits T

A

= T

J

= 25˚C.

Symbol

Parameter

Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

DC CHARACTERISTICS

I

CC

Supply Current

ADC08831

CLK = high

CS = V

CC

0.6

1.0

mA (max)

CS = LOW

1.7

2.4

mA (max)

I

CC

Supply Current

ADC08832

CLK = high (Note 16)

CS = V

CC

1.3

1.8

mA (max)

CS = LOW

2.4

3.5

mA (max)

Electrical Characteristics

The following specifications apply for V

CC

= V

REF

= +5 V

DC

, and t

r

= t

f

= 20 ns unless otherwise specified. Boldface limits

apply for T

A

= T

J

= T

MIN

to T

MAX

; all other limits T

A

= T

J

= 25˚C.

Symbol

Parameter

Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

f

CLK

Clock Frequency

2

MHz (max)

Clock Duty Cycle

(Note 14)

40

60

% (min)

% (max)

T

C

Conversion Time (Not Including MUX

Addressing Time)

f

CLK

= 2MHz

8

4

1/f

CLK

(max)

µs (max)

t

CA

Acquisition Time

1

⁄

2

1/f

CLK

(max)

t

SET-UP

CS Falling Edge or Data Input

Valid to CLK Rising Edge

25

ns (min)

t

HOLD

Data Input Valid after CLK

Rising Edge

20

ns (min)

t

pd1

, t

pd0

CLK Falling Edge to Output

Data Valid (Note 15)

C

L

= 100 pF:

Data MSB First

Data LSB First

250

200

ns (max)

ns (max)

t

1H

, t

0H

TRI-STATE Delay from Rising Edge

of CS to Data Output and SARS Hi-Z

C

L

= 10 pF, R

L

= 10 k

Ω

(see TRI-STATE Test Circuits)

50

ns

C

L

= 100 pF, R

L

= 2 k

Ω

180

ns (max)

C

IN

Capacitance of Analog input (Note 17)

13

pF

C

IN

Capacitance of Logic Inputs

5

pF

C

OUT

Capacitance of Logic Outputs

5

pF

www.national.com

4