Preliminary w78c52d – Rainbow Electronics W78C52D User Manual

Page 8

Preliminary W78C52D

- 8 -

The time-out period is obtained using the following formula:

1

2

1000 12

14

OSC

PRESCALER

Ч

Ч

Ч

Ч mS

Before Watchdog time-out occurs, the program must clear the 14-bit timer by writing 1 to WDTC.6

(CLRW). After 1 is written to this bit, the 14-bit timer , prescaler and this bit will be reset on the next

instruction cycle. The Watchdog timer is cleared on reset.

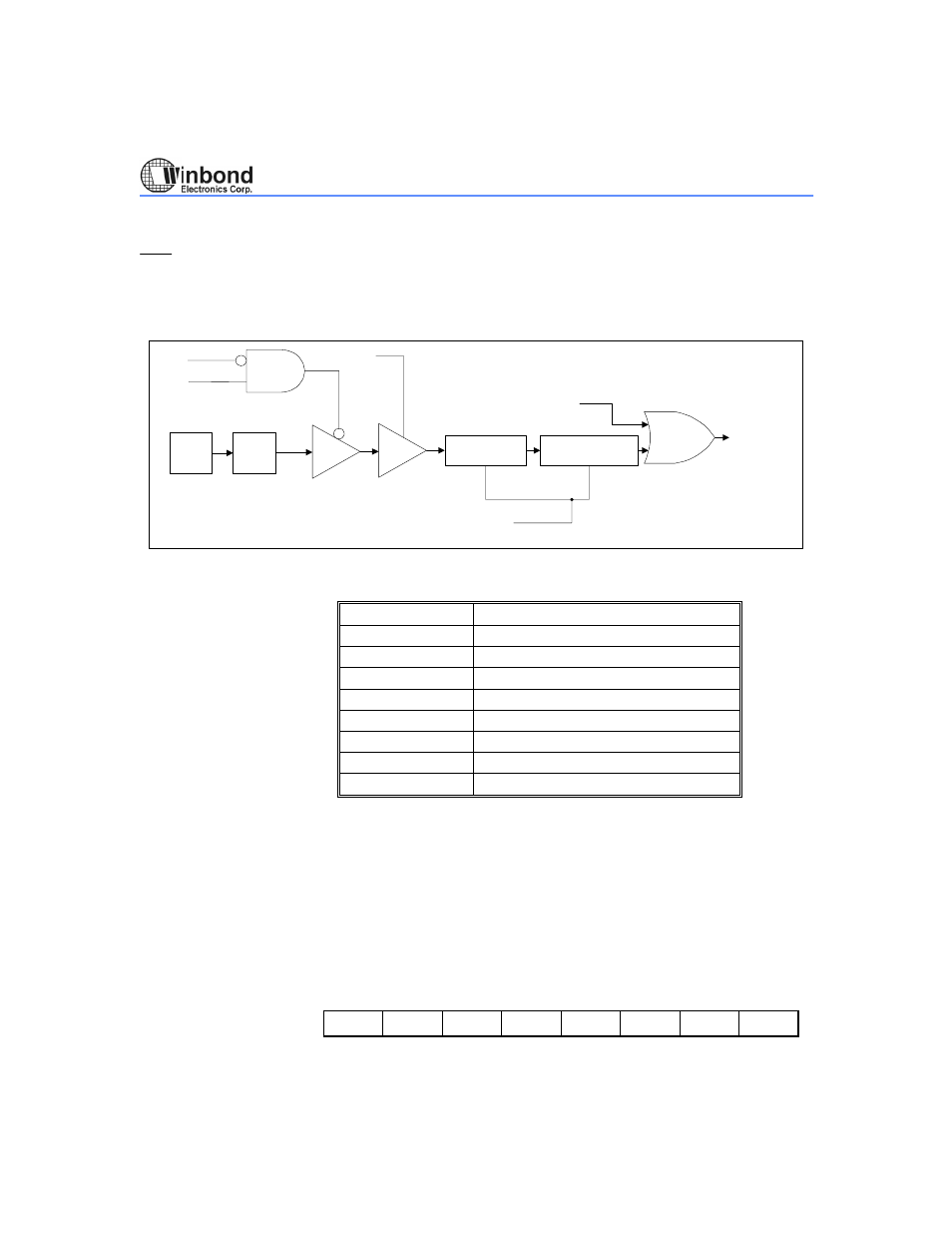

OSC

1/12

PRESCALER

14-BIT TIMER

CLEAR

CLRW

EXTERNAL

RESET

INTERNAL

RESET

WIDL

IDLE

ENW

Watchdog Timer Block Diagram

Typical Watchdog time-out period when OSC = 20 MHz

PS2 PS1 PS0

WATCHDOG TIME-OUT PERIOD

0 0 0

19.66 mS

0 1 0

39.32 mS

0 0 1

78.64 mS

0 1 1

157.28 mS

1 0 0

314.57 mS

1 0 1

629.14 mS

1 1 0

1.25 S

1 1 1

2.50 S

Reduce EMI Emission

Because of the on-chip ROM, when a program is running in internal ROM space, the ALE will be

unused. The transition of ALE will cause noise, so it can be turned off to reduce the EMI emission if it

is not needed. Turning off the ALE signal transition only requires setting the bit 0 of the AUXR SFR,

which is located at 08Eh. When ALE is turned off, it will be reactivated when the program accesses

external ROM/RAM data or jumps to execute an external ROM code. The ALE signal will turn off

again after it has been completely accessed or the program returns to internal ROM code space.

AUXR - Auxiliary Register

Bit:

7

6

5

4

3

2

1

0

-

-

-

-

-

-

-

AO

Mnemonic: AUXR

Address: 8Eh

AO:

Turn off ALE signal.