Preliminary w78c52d – Rainbow Electronics W78C52D User Manual

Page 6

Preliminary W78C52D

- 6 -

deglitch the reset line when the W78C52D is used with an external RC network. The reset logic also

has a special glitch removal circuit that ignores glitches on the reset line. During reset, the ports are

initialized to FFH, the stack pointer to 07H, PCON (with the exception of bit 4) to 00H, and all of the

other SFR registers except SBUF to 00H. SBUF is not reset.

New Defined Peripheral

In order to be more suitable for I/O, an extra 4-bit bit-addressable port P4 and two external interrupts

INT2

, INT3 have been added to either the PLCC or QFP package. And description follows:

1.

INT2

/ INT3

Two additional external interrupts,

INT2

and INT3 , whose functions are similar to those of external

interrupt 0 and 1 in the standard 80C52. The functions/status of these interrupts are

determined/shown by the bits in the XICON (External Interrupt Control) register. The XICON register

is bit-addressable but is not a standard register in the standard 80C52. Its address is at 0C0H. To

set/clear bits in the XICON register, one can use the "SETB (/CLR) bit" instruction. For example,

"SETB 0C2H" sets the EX2 bit of XICON.

***XICON - external interrupt control (C0H)

PX3

EX3

IE3

IT3

PX2

EX2

IE2

IT2

PX3: External interrupt 3 priority high if set

EX3: External interrupt 3 enable if set

IE3: If IT3 = 1, IE3 is set/cleared automatically by hardware when interrupt is detected/serviced

IT3: External interrupt 3 is falling-edge/low-level triggered when this bit is set/cleared by software

PX2: External interrupt 2 priority high if set

EX2: External interrupt 2 enable if set

IE2: If IT2 = 1, IE2 is set/cleared automatically by hardware when interrupt is detected/serviced

IT2: External interrupt 2 is falling-edge/low-level triggered when this bit is set/cleared by software

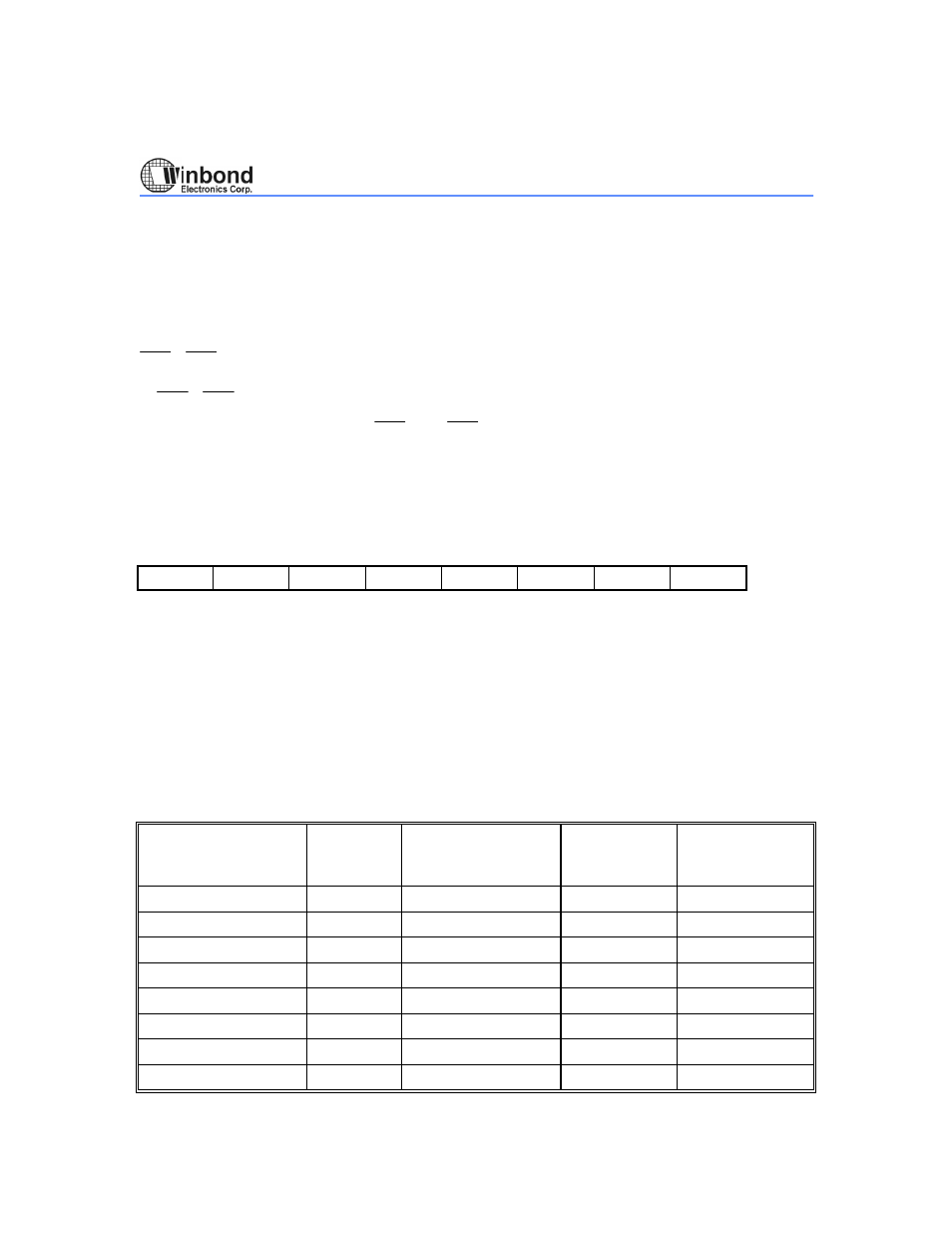

Eight-source interrupt informations:

INTERRUPT

SOURCE

VECTOR

ADDRESS

POLLING

SEQUENCE WITHIN

PRIORITY LEVEL

ENABLE

REQUIRED

SETTINGS

INTERRUPT

TYPE

EDGE/LEVEL

External Interrupt 0

03H

0 (highest)

IE.0

TCON.0

Timer/Counter 0

0BH

1

IE.1

-

External Interrupt 1

13H

2

IE.2

TCON.2

Timer/Counter 1

1BH

3

IE.3

-

Serial Port

23H

4

IE.4

-

Timer/Counter 2

2BH

5

IE.5

-

External Interrupt 2

33H

6

XICON.2

XICON.0

External Interrupt 3

3BH

7 (lowest)

XICON.6

XICON.3