Electrical characteristics (continued) – Rainbow Electronics MAX7502 User Manual

Page 3

MAX7500/MAX7501/MAX7502

Digital Temperature Sensors and Thermal

Watchdog with Bus Lockup Protection

_______________________________________________________________________________________

3

Note 4:

All parts operate properly over the +V

S

= 3V to 5V supply voltage range. The devices are tested and specified for rated

accuracy at their nominal supply voltage. Accuracy typically degrades 1°C per volt of change in +V

S

as it varies from the

nominal value.

Note 5:

All parameters are measured at +25°C. Values over the temperature range are guaranteed by design.

Note 6:

This specification indicates how often temperature data is updated. The devices can be read at any time without regard

to conversion state, while yielding the last conversion result.

Note 7:

For best accuracy, minimize output loading. Higher sink currents can affect sensor accuracy due to internal heating.

Note 8:

OS delay is user programmable up to six “over-limit” conversions before OS is set to minimize false tripping in noisy

environments.

Note 9:

Default values set at power-up.

Note 10:

All timing specifications are guaranteed by design.

Note 11:

A master device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL’s

falling edge.

Note 12:

C

B

= total capacitance of one bus line in pF. Tested with C

B

= 400pF.

Note 13:

Input filters on SDA, SCL, and A_ suppress noise spikes less than 50ns.

Note 14:

Holding the SDA line low for a time greater than t

TIMEOUT

causes the devices to reset SDA to the IDLE state of the serial

bus communication (SDA set high).

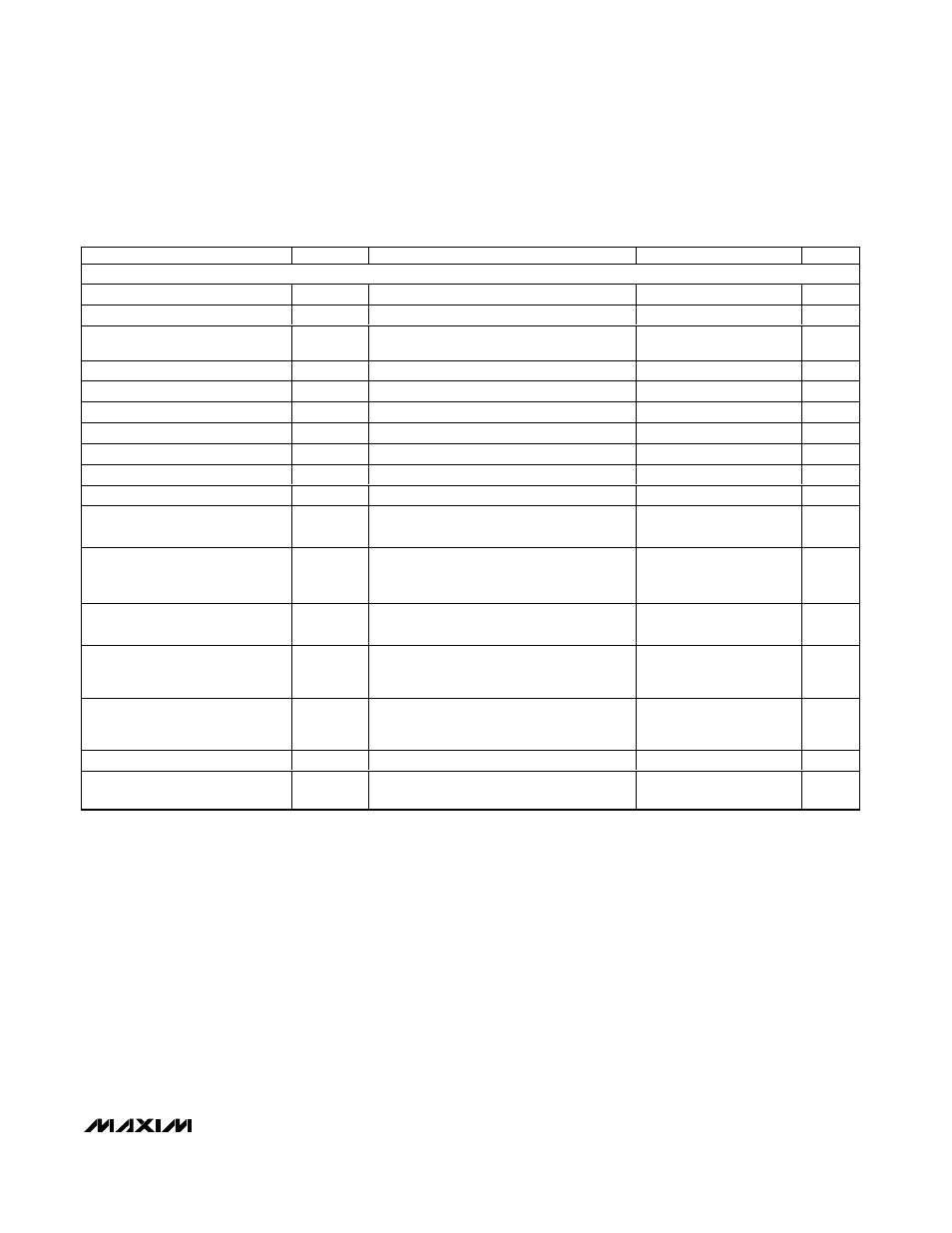

ELECTRICAL CHARACTERISTICS (continued)

(+V

S

= +3.0V to +5.5V, T

A

= -55

°C to +125°C, unless otherwise noted. Typical values are at +V

S

= +5V, T

A

= +25

°C.) (Notes 4, 5)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

I

2

C-COMPATIBLE TIMING (Note 10)

Serial Clock Frequency

f

SCL

Bus timeout inactive

DC

400

kHz

Minimum RESET Pulse Width

1

µs

Bus Free Time Between STOP

and START Conditions

t

BUF

1.3

µs

START Condition Hold Time

t

HD:STA

0.6

µs

STOP Condition Setup Time

t

SU:STO

90% of SCL to 10% of SDA

100

ns

Clock Low Period

t

LOW

1.3

µs

Clock High Period

t

HIGH

0.6

µs

START Condition Setup Time

t

SU:STA

90% of SCL to 90% of SDA

100

ns

Data Setup Time

t

SU:DAT

10% of SDA to 10% of SCL

100

ns

Data Hold Time

t

HD:DAT

10% of SCL to 10% of SDA (Note 11)

0

0.9

µs

Maximum Receive SCL/SDA Rise

Time

t

R

300

ns

Minimum Receive SCL/SDA Rise

Time

t

R

(Note 12)

20 +

0.1 x

C

B

ns

Maximum Receive SCL/SDA Fall

Time

t

F

300

ns

Minimum Receive SCL/SDA Fall

Time

t

F

(Note 12)

20 +

0.1 x

C

B

ns

Transmit SDA Fall Time

t

F

(Note 12)

20 +

0.1 x

C

B

250

ns

Pulse Width of Suppressed Spike

t

SP

(Note 13)

0

50

ns

SDA Time Low for Reset of Serial

Interface

t

TIMEOUT

(Note 14)

150

300

ms