Rainbow Electronics MAX5102 User Manual

General description, Applications, Features

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

General Description

The MAX5102 parallel-input, voltage-output, dual 8-bit

digital-to-analog converter (DAC) operates from a single

+2.7V to +5.5V supply and comes in a space-saving

16-pin TSSOP package. Internal precision buffers

swing Rail-to-Rail

®

, and the reference input range

includes both ground and the positive rail. Both DACs

share a common reference input.

The MAX5102 has separate input latches for each of its

DACs. Data is transferred to the input latches from a

common 8-bit input port. The DACs are individually

selected through address input A0 and are updated by

bringing WR low.

The MAX5102 features a shutdown mode that reduces

current to 1nA, as well as a power-on reset mode that

resets all registers to code 00 hex on power-up.

Applications

Digital Gain and Offset Adjustment

Programmable Attenuators

Portable Instruments

Power-Amp Bias Control

Features

♦ +2.7V to +5.5V Single-Supply Operation

♦ Ultra-Low Supply Current

0.2mA while Operating

1nA in Shutdown Mode

♦ Ultra-Small 16-Pin TSSOP Package

♦ Ground to V

DD

Reference Input Range

♦ Output Buffer Amplifiers Swing Rail-to-Rail

♦ Power-On Reset Sets All Registers to Zero

MAX5102

+2.7V to +5.5V, Low-Power, Dual, Parallel

8-Bit DAC with Rail-to-Rail Voltage Outputs

________________________________________________________________ Maxim Integrated Products

1

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

V

DD

OUTA

OUTB

GND

A0

D0

D1

D2

D3

TOP VIEW

MAX5102

TSSOP

REF

SHDN

D6

WR

D7

D5

D4

19-1565; Rev 0; 10/99

PART

MAX5102AEUE

MAX5102BEUE

-40°C to +85°C

-40°C to +85°C

TEMP. RANGE

PIN-PACKAGE

16 TSSOP

16 TSSOP

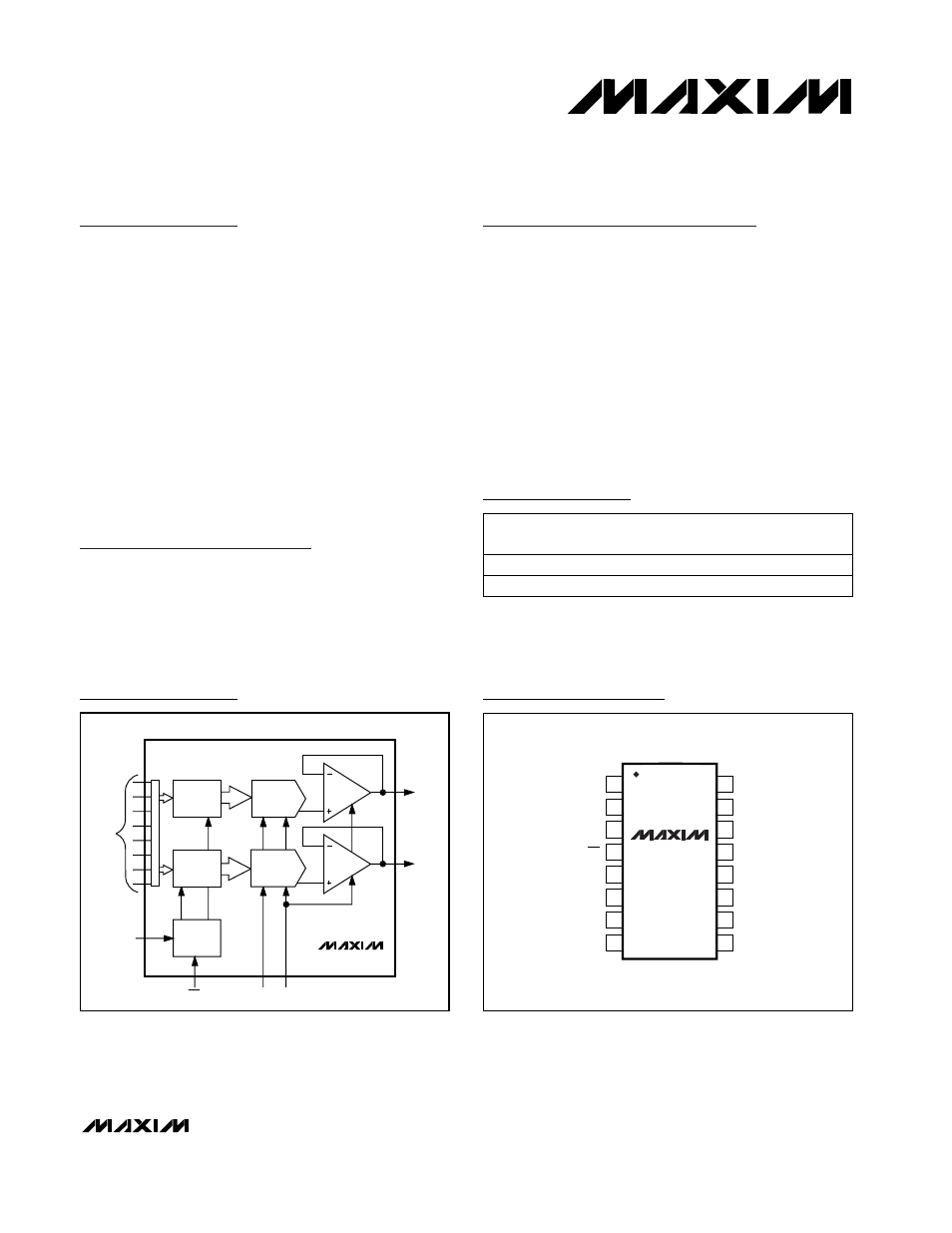

Pin Configuration

Ordering Information

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

INL

(LSB)

±1

±2

OUTA

OUTB

MAX5102

DAC A

DAC B

INPUT

LATCH A

INPUT

LATCH B

CONTROL

LOGIC

SHDN

REF

A0

WR

D0–D7

Functional Diagram