Pin description – Rainbow Electronics MAX8805Z User Manual

Page 11

MAX8805Y/MAX8805Z

600mA PWM Step-Down Converters in

2mm x 2mm WLP for WCDMA PA Power

______________________________________________________________________________________

11

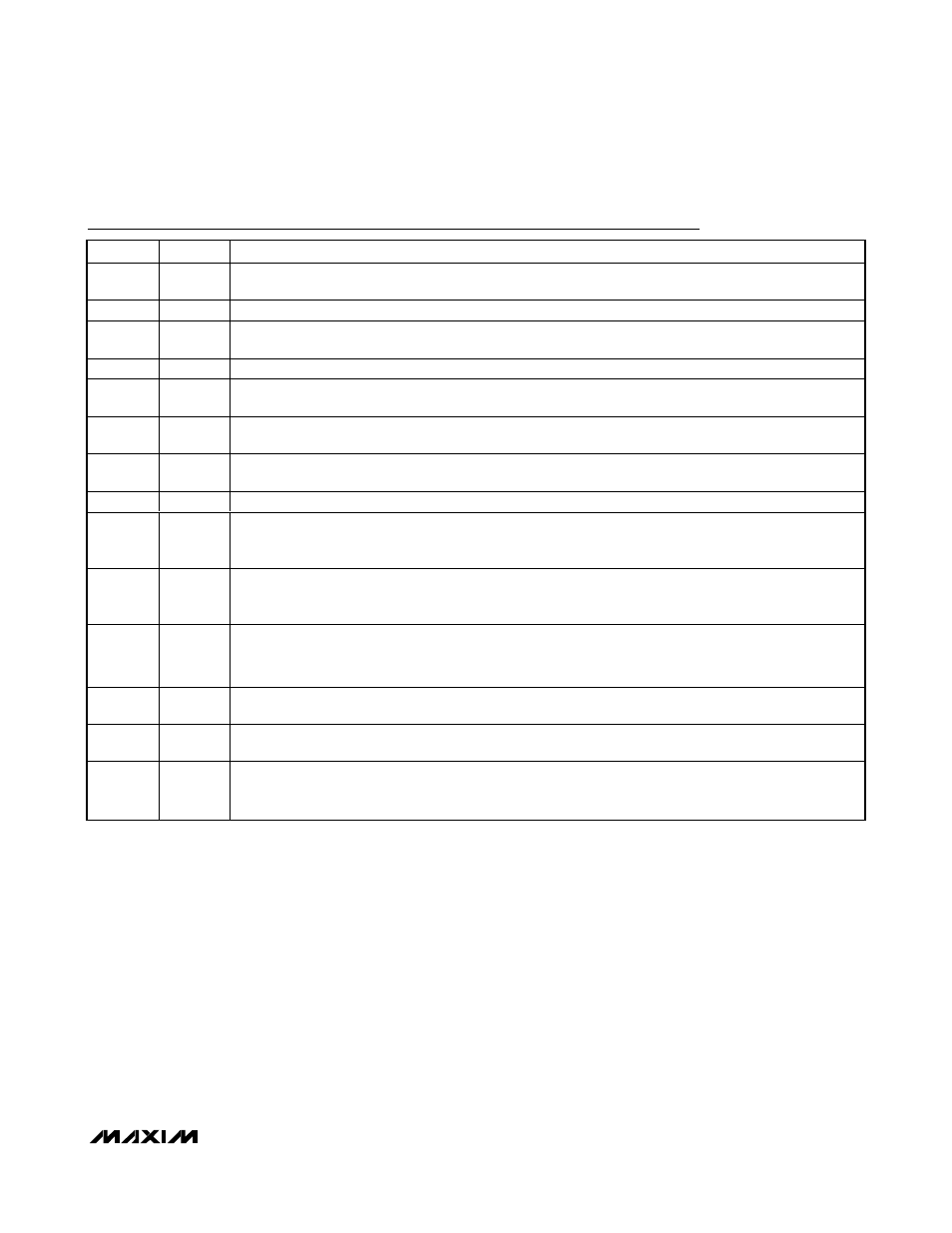

Pin Description

PIN

NAME

FUNCTION

A1

REFBP

Reference Noise Bypass. Bypass REFBP to AGND with a 0.22µF ceramic capacitor to reduce noise on the

LDO outputs. REFBP is internally pulled down through a 1k

Ω resistor during shutdown.

A2

AGND

Low-Noise Analog Ground

A3

REFIN

DAC-Controlled Input. The output of the PA step-down converter is regulated to 2 x V

REFIN

. When V

REFIN

reaches 0.465 x V

IN2

, bypass mode is enabled.

A4

PGND

Power Ground for PA Step-Down Converter

B1

LDO2

200mA LDO Regulator 2 Output. Bypass LDO2 with a 1µF ceramic capacitor as close as possible to LDO2

and AGND. LDO2 is internally pulled down through a 1k

Ω resistor when this regulator is disabled.

B2

PA_EN

PA Step-Down Converter Enable Input. Connect to IN_ or logic-high for normal operation. Connect to GND

or logic-low for shutdown mode.

B3

EN2

LDO2 Enable Input. Connect to IN2 or logic-high for normal operation. Connect to AGND or logic-low for

shutdown mode.

B4

LX

Inductor Connection. Connect an inductor from LX to the output of the PA step-down converter.

C1

IN2

Supply Voltage Input for LDO1, LDO2, and Internal Reference. Connect IN2 to a battery or supply voltage

from 2.7V to 5.5V. Bypass IN2 with a 2.2µF ceramic capacitor as close as possible to IN2 and AGND.

Connect IN2 to the same source as IN1A and IN1B.

C2

HP

High-Power Mode Set Input. Drive HP high to invoke forced bypass mode. Bypass mode connects the

input of the PA step-down converter directly to its output through the internal bypass MOSFET. Drive HP

low to disable the forced bypass mode.

C3, C4

IN1B,

IN1A

Supply Voltage Input for PA Step-Down Converter. Connect IN1_ to a battery or supply voltage from 2.7V to

5.5V. Bypass the connection of IN1_ with a 2.2µF ceramic capacitor as close as possible to IN1_, and

PGND. IN1A

and IN1B are internally connected together. Connect IN1_ to the same source as IN2.

D1

LDO1

200mA LDO Regulator 1 Output. Bypass LDO1 with a 1µF ceramic capacitor as close as possible to LDO1

and AGND. LDO1 is internally pulled down through a 1k

Ω resistor when this regulator is disabled.

D2

EN1

LDO1 Enable Input. Connect to IN2 or logic-high for normal operation. Connect to AGND or logic-low for

shutdown mode.

D3, D4

PAB, PAA

PA Connection for Bypass Mode. Internally connected to IN1_ using the internal bypass MOSFET during

bypass mode. PA_ is connected to the internal feedback network. Bypass PA_ with a 2.2µF ceramic

capacitor as close as possible to PA_ and PGND.