Detailed description, Applications information – Rainbow Electronics MAX14541Е User Manual

Page 5

3-Channel, Low-Leakage ESD Protector

MAX14541E

_______________________________________________________________________________________ 5

________________Detailed Description

The MAX14541E low-leakage, low-capacitance, Q15kV

ESD-protection diode arrays are suitable for high-speed

and general-signal ESD protection. Low input capaci-

tance makes this device ideal for ESD protection of

high-speed signals. Each channel consists of a pair of

diodes that steer ESD current pulses to V

CC

or GND. The

MAX14541E is a 3-channel device (see the Functional

Diagram).

The MAX14541E is designed to work in conjunction with

a device’s intrinsic ESD protection. The MAX14541E

limits the excursion of the ESD event to below Q25V

peak voltage when subjected to the Human Body Model

waveform. When subjected to the IEC 61000-4-2 Contact

Discharge waveform, the peak voltage is limited to

Q

60V. The peak voltage is limited to Q100V when sub-

jected to Air-Gap Discharge. The device protected by

the MAX14541E must be able to withstand these peak

voltages, plus any additional voltage generated by the

parasitic of the board.

___________Applications Information

Design Considerations

Maximum protection against ESD damage results from

proper board layout (see the Layout Recommendations

section). A good layout reduces the parasitic series

inductance on the ground line, supply line, and protect-

ed signal lines. The MAX14541E ESD diodes clamp the

voltage on the protected lines during an ESD event and

shunt the current to GND or V

CC

. In an ideal circuit, the

clamping voltage (V

C

) is defined as the forward voltage

drop (V

F

) of the protection diode, plus any supply volt-

age present on the cathode.

For positive ESD pulses:

V

C

= V

CC

+ V

F

For negative ESD pulses:

V

C

= -V

F

The effect of the parasitic series inductance on the lines

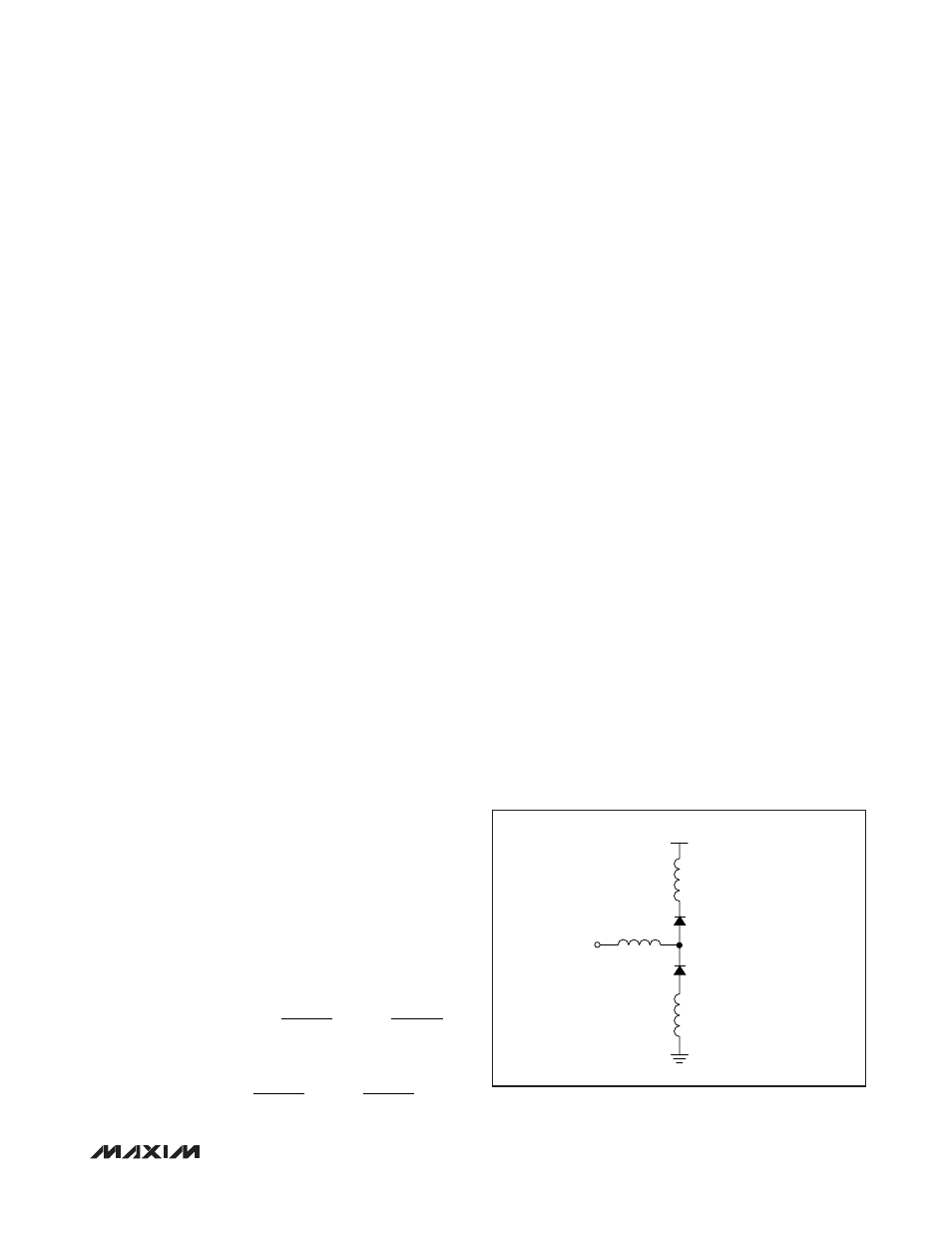

must also be considered (Figure 1).

For positive ESD pulses:

For negative ESD pulses:

where I

ESD

is the ESD current pulse.

During an ESD event, the current pulse rises from zero

to peak value in nanoseconds (Figure 2). For example,

in a +15kV IEC 61000-4-7 Air-Gap Discharge ESD event,

the pulse current rises to approximately 45A in 1ns

(di/dt = 45 x 10

9

). An inductance of only 10nH adds an

additional 450V to the clamp voltage, and represents

approximately 0.5in of board trace. Regardless of the

device’s specified diode clamp voltage, a poor layout

with parasitic inductance significantly increases the

effective clamp voltage at the protected signal line.

Minimize the effects of parasitic inductance by placing

the MAX14541E as close as possible to the connector

(or ESD contact point).

A low-ESR 0.1FF capacitor is required between V

CC

and

GND to get the maximum ESD protection possible. This

bypass capacitor absorbs the charge transferred by a

positive ESD event. Ideally, the supply rail (V

CC

) would

absorb the charge caused by a positive ESD strike

without changing its regulated value. All power supplies

have an effective output impedance on their positive

rails. If a power supply’s effective output impedance is

1I, then by using V = I x R, the clamping voltage of V

C

increases by the equation V

C

= I

ESD

x R

OUT

. A +8kV IEC

61000-4-2 ESD event generates a current spike of 24A.

The clamping voltage increases by V

C

= 24A x 1I, or

V

C

= 24V. Again, a poor layout without proper bypassing

increases the clamping voltage. A ceramic chip capaci-

tor mounted as close as possible to the MAX14541E

V

CC

pin is the best choice for this application. A bypass

capacitor should also be placed as close as possible to

the protected device.

(

)

ESD

ESD

C

CC

F(D1)

d I

d(I

)

V

V

V

L1

L2

dt

dt

=

+

+

Ч

+

Ч

ESD

ESD

C

F(D2)

d(I

)

d(I

)

V

V

L1

L3

dt

dt

= −

+

Ч

+

Ч

Figure 1. Parasitic Series Inductance

L1

PROTECTED

LINE

L3

D2

GROUND RAIL

POSITIVE SUPPLY RAIL

I/O_

D1

L2