Grounding and power-supply decoupling – Rainbow Electronics MAX5184 User Manual

Page 14

MAX5181/MAX5184

10-Bit, 40MHz, Current/Voltage-Output DACs

14

______________________________________________________________________________________

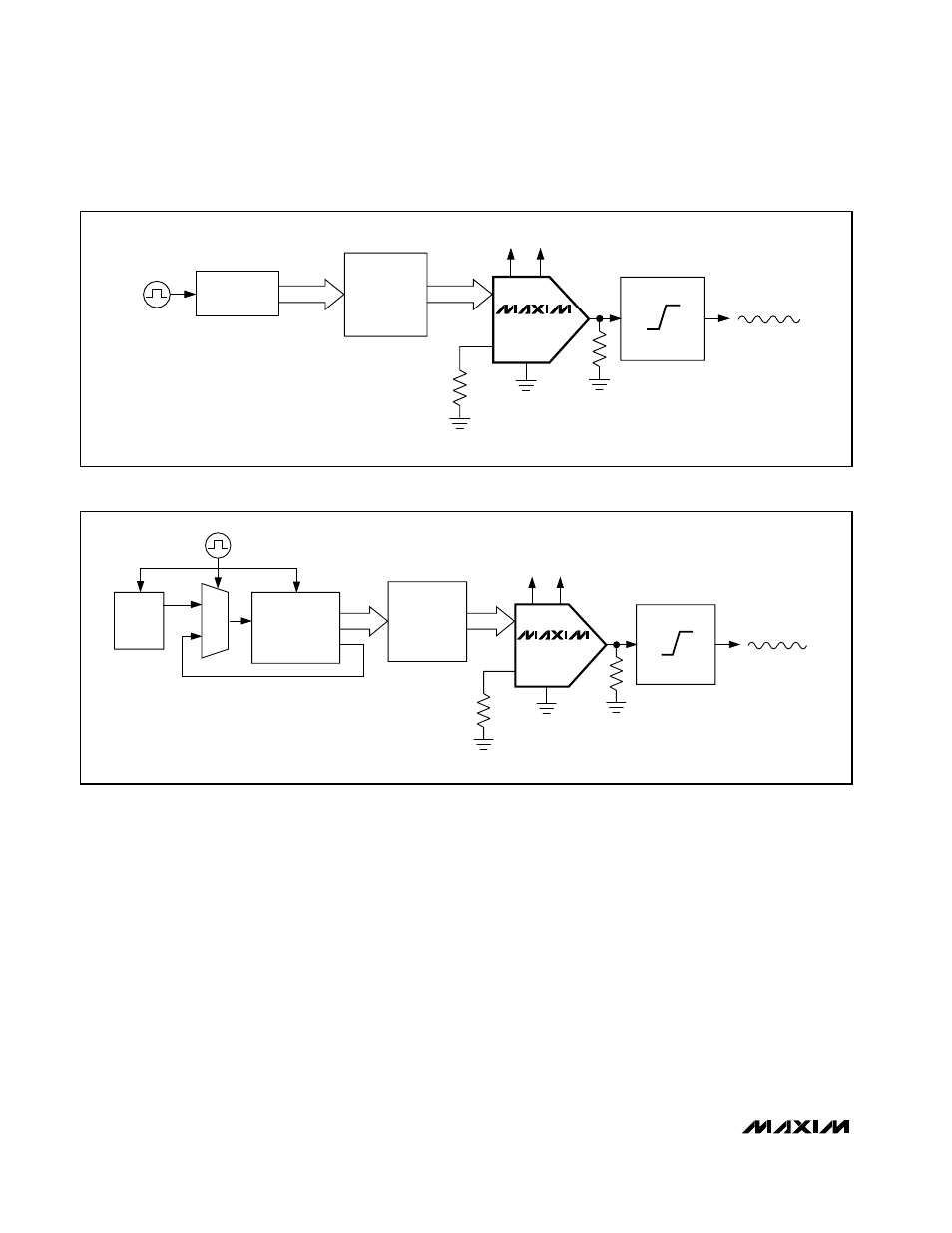

relaxed requirements in resolution (10-bit AWGs). To

increase an AWG’s high-frequency accuracy, tempera-

ture stability, wide-band tuning, and past phase-contin-

uos frequency switching, the user may approach a

direct digital synthesis (DDS) AWG (Figure 8b). This

DDS loop supports standard waveforms that are repeti-

tive, such as sine, square, TTL, and triangular wave-

forms. DDS allows for precise control of the

data-stream input to the DAC. Data for one complete

output waveform cycle is sequentially stored in a RAM.

As the RAM addresses are changing, the DAC con-

verts the incoming data bits into a corresponding volt-

age waveform. The resulting output signal frequency is

proportional to the frequency rate at which the RAM

addresses are changed.

Grounding and Power-Supply Decoupling

Grounding and power-supply decoupling strongly influ-

ence the MAX5181/MAX5184’s performance. Unwanted

digital crosstalk may couple through the input, refer-

ence, power-supply, and ground connections, which

may affect dynamic specifications like SNR or SFDR. In

addition, electromagnetic interference (EMI) can either

couple into or be generated by the MAX5181/

MAX5184. Therefore, grounding and power-supply

decoupling guidelines for high-speed, high-frequency

applications should be closely followed.

First, a multilayer PC board with separate ground and

power-supply planes is recommended. High-speed

signals should be run on controlled impedance lines

Figure 8b. Direct Digital Synthesis AWG

Figure 8a. Traditional Arbitrary Waveform Generation

9.6k*

400

Ω*

WAVEFORM

MEMORY

(RAM)

DV

DD

AV

DD

*MAX5181 ONLY

MAX5181

MAX5184

10

ADR

FILTERED

WAVEFORM

(ANALOG OUTPUT)

LOWPASS

RECONSTRUCTION

FILTER

VARIABLE

fc

COUNTER

CLOCK

GENERATOR

DATA

9.6k*

400

Ω*

WAVEFORM

MEMORY

(RAM)

DV

DD

AV

DD

*MAX5181 ONLY

MAX5181

MAX5184

10

DATA

ADR

A

D

D

E

R

FILTERED

WAVEFORM

(ANALOG OUTPUT)

LOWPASS

RECONSTRUCTION

FILTER

VARIABLE

fc

PHASE

ACCUMULATOR

ACCUMULATOR

FEEDBACK LOOP

FOR DATA BITS

CLOCK

GENERATOR

PIR

PHASE

INCREMENT

REGISTER