St380chpbf series, Vishay high power products, On-state conduction – C&H Technology ST380CHPbF Series User Manual

Page 3: Switching, Blocking

www.vishay.com

For technical questions, contact: [email protected]

Document Number: 94411

2

Revision: 06-May-08

ST380CHPbF Series

Vishay High Power Products

Phase Control Thyristors

(Hockey PUK Version), 960 A

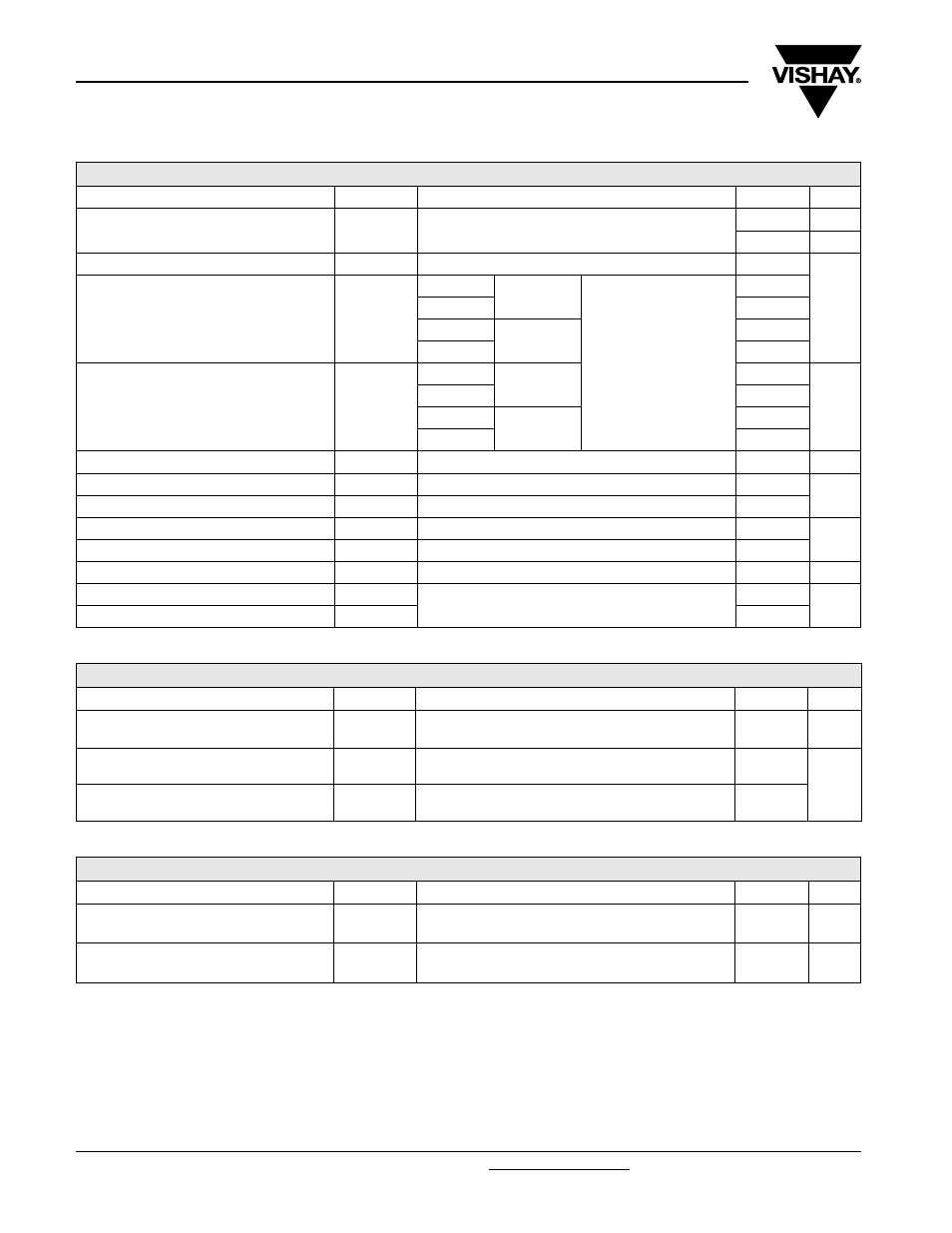

ON-STATE CONDUCTION

PARAMETER SYMBOL

TEST

CONDITIONS

VALUES

UNITS

Maximum average on-state current

at heatsink temperature

I

T(AV)

180° conduction, half sine wave

double side (single side) cooled

960 (440)

A

80 (110)

°C

Maximum RMS on-state current

I

T(RMS)

DC at 25 °C heatsink temperature double side cooled

2220

A

Maximum peak, one-cycle

non-repetitive surge current

I

TSM

t = 10 ms

No voltage

reapplied

Sinusoidal half wave,

initial T

J

= T

J

maximum

12 500

t = 8.3 ms

13 000

t = 10 ms

100 % V

RRM

reapplied

10 500

t = 8.3 ms

11 000

Maximum I

2

t for fusing

I

2

t

t = 10 ms

No voltage

reapplied

782

kA

2

s

t = 8.3 ms

713

t = 10 ms

100 % V

RRM

reapplied

553

t = 8.3 ms

505

Maximum I

2

√t for fusing

I

2

√t

t = 0.1 to 10 ms, no voltage reapplied

7820

kA

2

√s

Low level value of threshold voltage

V

T(TO)1

(16.7 % x

π x I

T(AV)

< I <

π x I

T(AV)

), T

J

= T

J

maximum

0.85

V

High level value of threshold voltage

V

T(TO)2

(I >

π x I

T(AV)

), T

J

= T

J

maximum

0.88

Low level value of on-state slope resistance

r

t1

(16.7 % x

π x I

T(AV)

< I <

π x I

T(AV)

), T

J

= T

J

maximum

0.25

m

Ω

High level value of on-state slope resistance

r

t2

(I >

π x I

T(AV)

), T

J

= T

J

maximum

0.24

Maximum on-state voltage

V

TM

I

pk

= 2900 A, T

J

= T

J

maximum, t

p

= 10 ms sine pulse

1.58

V

Maximum holding current

I

H

T

J

= 25 °C, anode supply 12 V resistive load

600

mA

Typical latching current

I

L

1000

SWITCHING

PARAMETER SYMBOL

TEST

CONDITIONS

VALUES

UNITS

Maximum non-repetitive rate of rise

of turned-on current

dI/dt

Gate drive 20 V, 20

Ω, t

r

≤ 1 µs

T

J

= T

J

maximum, anode voltage

≤ 80 % V

DRM

1000

A/µs

Typical delay time

t

d

Gate current 1 A, dI

g

/dt = 1 A/µs

V

d

= 0.67 % V

DRM

, T

J

= 25 °C

1.0

µs

Typical turn-off time

t

q

I

TM

= 550 A, T

J

= T

J

maximum, dI/dt = 40 A/µs,

V

R

= 50 V, dV/dt = 20 V/µs, gate 0 V 100

Ω, t

p

= 500 µs

100

BLOCKING

PARAMETER SYMBOL

TEST

CONDITIONS

VALUES

UNITS

Maximum critical rate of rise of

off-state voltage

dV/dt

T

J

= T

J

maximum linear to 80 % rated V

DRM

500

V/µs

Maximum peak reverse and

off-state leakage current

I

RRM

,

I

DRM

T

J

= T

J

maximum, rated V

DRM

/V

RRM

applied

100

mA