Component_name>/implement, Component_name>/implement/results, Component_name>/simulation – Xilinx LogiCORE IP CAN 3.2 User Manual

Page 20

20

CAN Getting Started Guide

UG186 April 19, 2010

Chapter 4: Detailed Example Design

The implement directory contains the core implementation script files. Generated for Full-

System Hardware Evaluation and Full license types.

The results directory is created by the implement script, after which the implement script

results are placed in the results directory.

The simulation directory contains the simulation scripts provided with the core.

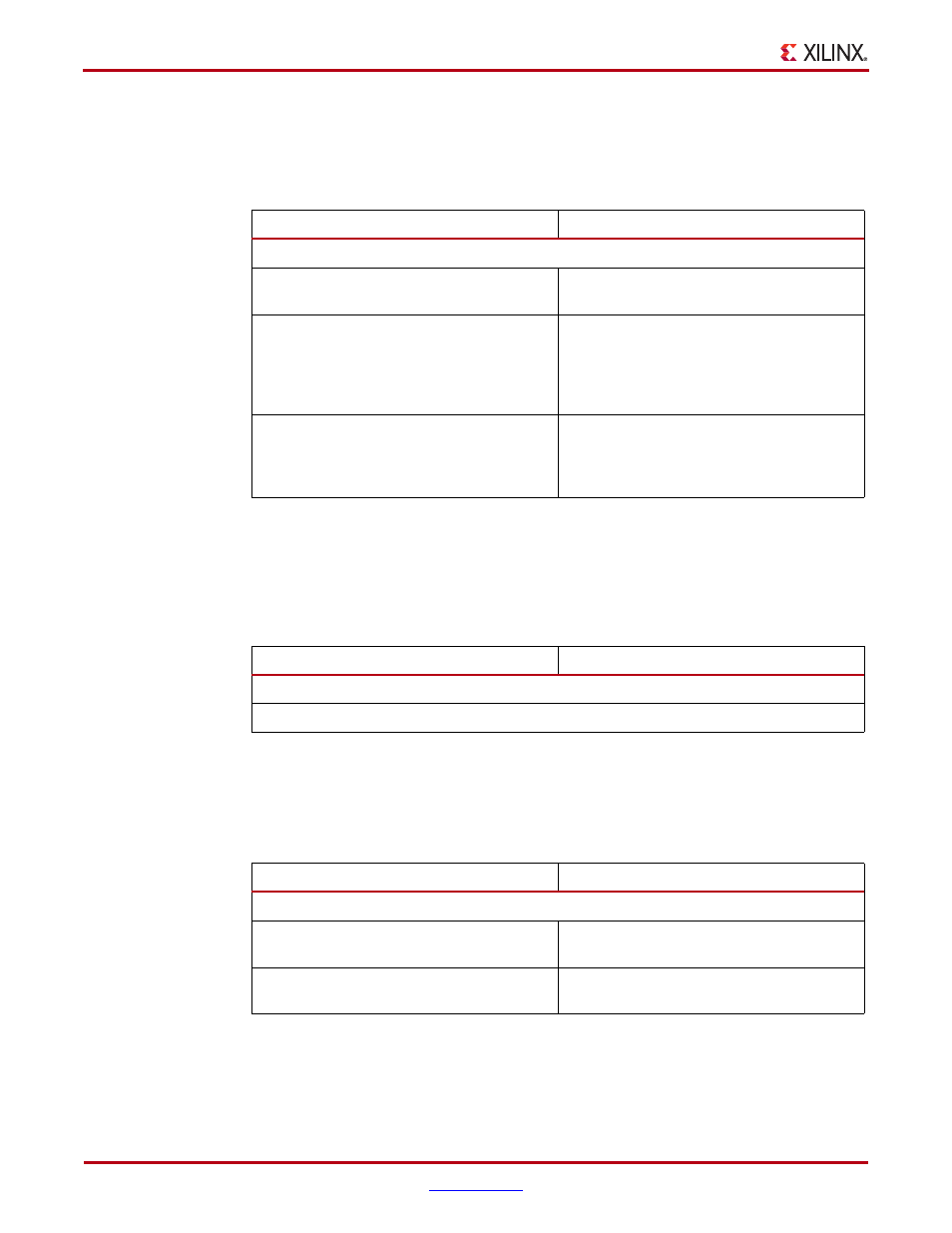

Table 4-5:

Implement Directory

Name

Description

implement.{bat|sh}

A Windows (.bat) or Linux script that

processes the example design.

xst.prj

The XST project file for the example design

that lists all of the source files to be

synthesized. Only available when the CORE

Generator software project option is set to

ISE® or Other.

xst.scr

The XST script file for the example design

used to synthesize the core. Only available

when the CORE Generator software Vendor

project option is set to ISE or Other.

Table 4-6:

Results Directory

Name

Description

Implement script result files.

Table 4-7:

Simulation Directory

Name

Description

glbl.v

Verilog test file provided with the

demonstration test bench.

can_v3_2_tb.v[hd]

Verilog/VHDL test file provided with the

demonstration test bench.