Toshiba SD-R5112 User Manual

Page 23

16/29

SD-R5112 Rev.1.0

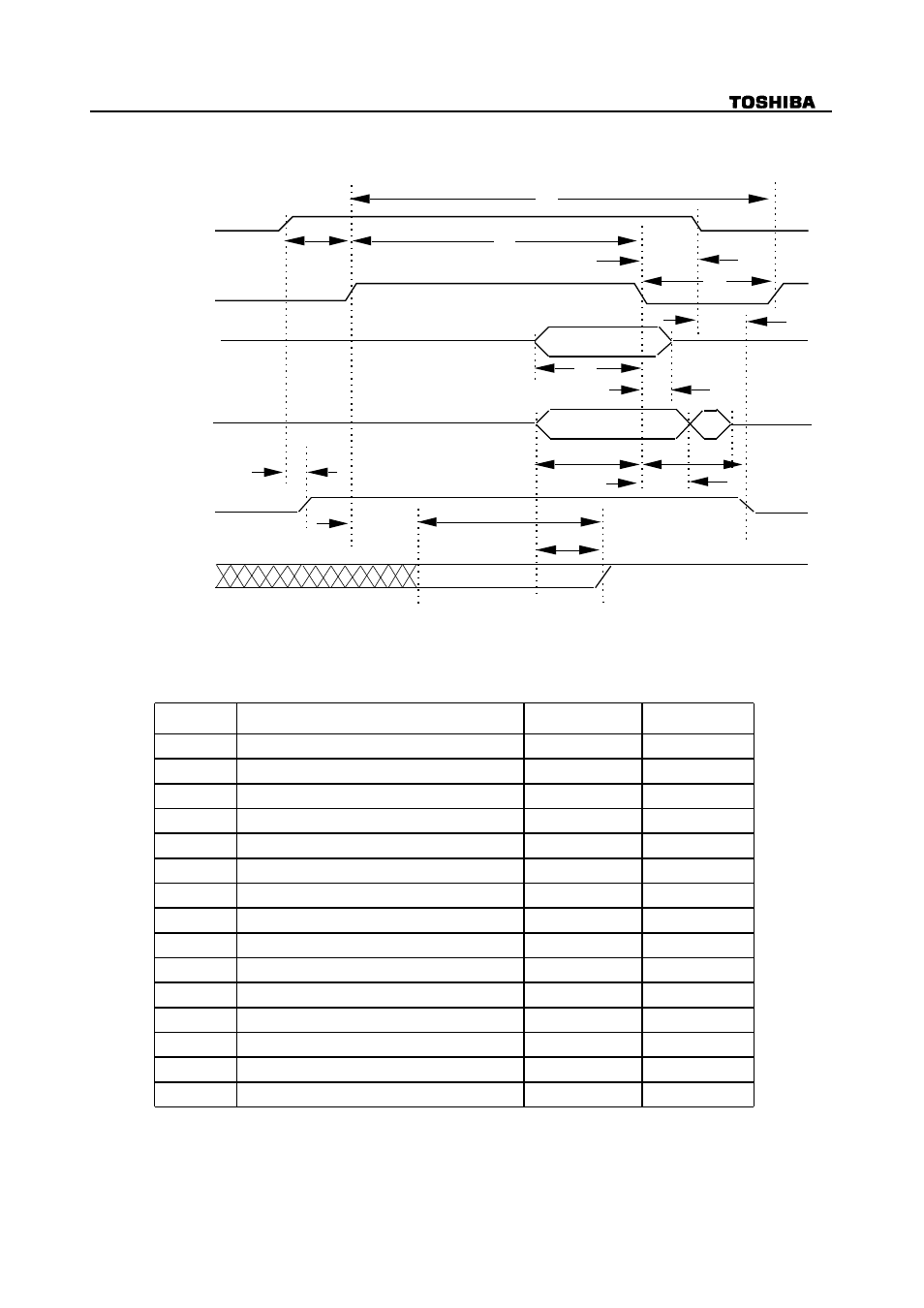

6.2.2. Timing of Host Interface (PIO)

Figure 10 shows the Host Interface Timings.

Address valid*1

DIOR-/DIOW-

Write data valid*2

Read data valid*2

IOCS16-

IORDY

t4

t6

t7

t9

tA

t8

t1

t5

tB

tRD

t6Z

*1:Device Address consists of signals CS0-, CS1-, and DA2-0

*2:Data consists of DD0-15 (16-bit) or DD0-7 (8-bit)

t0

t2

t3

t2i

PIO timing parameters min (ns) max (ns)

Min Time (ns)

Max Time (ns)

t0

Cycle time

120

t1

Address valid to DIOR/DIOW-setup

25

t2

DIOR/DIOW-pulse wide

70

t2i

DIOR/DIOW-recovery time

25

t3

DIOW-data setup

20

t4

DIOW-data hold

10

t5

DIOR-data setup

20

t6

DIOR-data hold

5

t6Z

DIOR-data tristate

30

t7

Addr valid to IOCS 16-assertion

30

t8

Addr valid to IOCS 16-negation

30

t9

DIOR/DIOW-to address valid hold

10

tRD

Read Data Valid to IORDY active

0

tA

IORDY setup time

35

tB

IORDY pulse wide

1250

Figure 10 Host Interface Timing

- DR430KU (103 pages)

- SD-6980SY (76 pages)

- RD-XS32SB (239 pages)

- SD-P1707SR (76 pages)

- SD-2200 (48 pages)

- DVD - ROM MOBILE DRIVE SD-C2732 (12 pages)

- MD20F52 (56 pages)

- MD20FN3/R (48 pages)

- HD-A35KU (46 pages)

- MW20FN3/R (68 pages)

- HD-A2KC (72 pages)

- HD-A20KC (76 pages)

- HD-A30KU (48 pages)

- SD-W1111 (34 pages)

- MW24F12 (2 pages)

- MD20FM1 (2 pages)

- MV19N2 (2 pages)

- DVD Video Player SD-V394SU (72 pages)

- M750 (2 pages)

- SD-9200 (70 pages)

- MW14F52 (2 pages)

- MW 26G71 (2 pages)

- MV13N2/W (56 pages)

- SD-480EKE (40 pages)

- SD-3980 (2 pages)

- MV 13N2 (2 pages)

- 37HLX95 (106 pages)

- CASSETTE RECORDER SD-V393SU (68 pages)

- SD-6980 (2 pages)

- SD-2700 (51 pages)

- SD-150ESB (35 pages)

- 9676109606 (48 pages)

- SD-240ESB (61 pages)

- SD-K600 (51 pages)

- SD-V290 (2 pages)

- D-R1 (2 pages)

- SD-260SY (61 pages)

- MD13P3 (48 pages)

- DVd Video Recorder D-R4SU (131 pages)

- MD20FN1/R (48 pages)

- MD13N3R (47 pages)

- 32LV17 (78 pages)

- MV13Q41 (2 pages)

- HD-EP30KB (40 pages)

- HD-EP30 (3 pages)