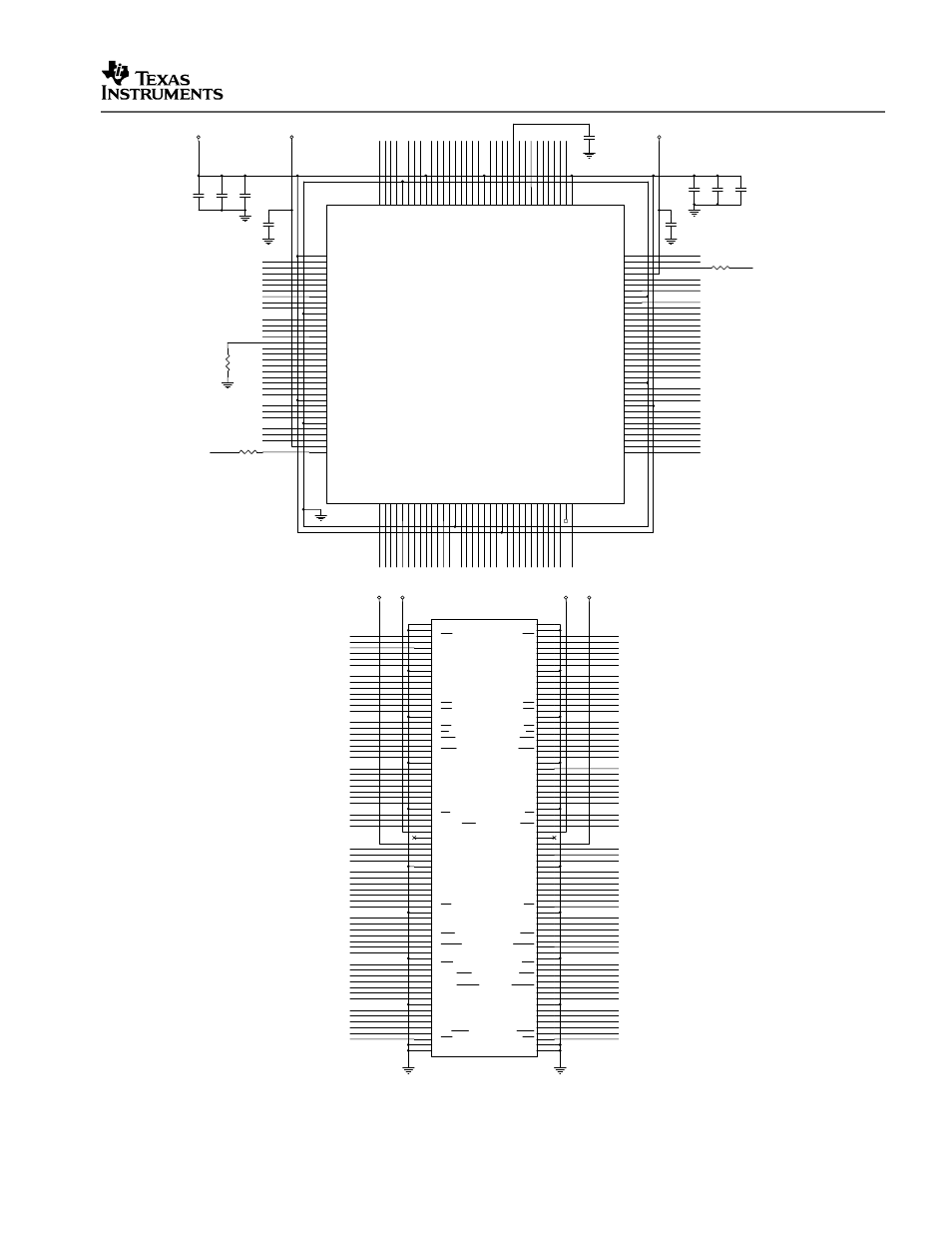

Figure 5. reference schematics – page 2 – Texas Instruments DUAL SOCKET PC CARD CONTROLLER PCI1520 User Manual

Page 23

SCPA033

PCI1520 Implementation Guide

23

Figure 5.

Reference Schematics – Page 2

A_OE#

B_

IN

PAC

K#

B_

A23

A_CD2#

A_D

2

A_A24

B_D13

A_A6

A_A13

B_

R

ESET

B_

D

8

A_D6

B_A11

B_A1

B_D2

A_A6

A_IOWR#

A_D4

B_CE2#

A_D9

A_A0

A_A5

B_

R

EAD

Y

B_

A1

B_IOWR#

B_

BVD

1

B

_

CD2

#

A_BVD1

B_D6

B_

D

1

A_A25

B_CE1#

A_D7

B_A4

A_A3

B_D13

B_WAIT#

B_A20

A_A2

A_D5

B_A11

C9

.1uF

B_D9

A_A19

C5

.1uF

A_A2

A_A20

R2

100

B_IORD#

A_D5

B_READY

B_A20

A_R

EAD

Y

A_D11

A_A17

A_VS1#

A_A19

A_D15

B_A9

B_D3

B_

VS1#

B_

A25

A_A8

A_D13

A_D7

B_A23

A_A15

A_D

0

A_VS2#

B_A12

B_WP

A_A21

A_CD1#

A_REG#

A_RESET

A_WAIT#

A_A15

AVCC

B_A7

A_D

9

B_D5

A_D3

A_A1

B_

A12

B_

D

9

A_W

A

IT

#

A_D

8

A_VS2#

U1B

PCI1520 (CARDBUS)

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

VCC

B_CCD1#//B_CD1#

B_CAD0//B_D3

B_CAD2//B_D11

B_CAD1//B_D4

B_CAD4//B_D12

B_CAD3//B_D5

B_CAD6//B_D13

B_CAD5//B_D6

B_RSVD//B_D14

GND

B_CAD7//B_D7

B_CAD8//B_D15

B_CC/BE0#//B_CE1#

B_CAD9//B_A10

VR_EN#

B_CAD10//B_CE2#

B_CAD11//B_OE#

B_CAD12//B_A11

B_CAD13//B_IORD#

B_CAD15//B_IOWR#

B_CAD14//B_A9

B_CAD16//B_A17

B_CC/BE1#//B_A8

B_RSVD//B_A18

VCC

B_CPAR//B_A13

B_CBLOCK#//B_A19

B_CPERR#//B_A14

GND

B_CSTOP#//B_A20

B_CGNT#//B_WE#

B_CDEVSEL#//B_A21

VCCB

B_CCLK//B_A16

B

_

CT

RDY

#

//

B

_

A

2

2

B

_

CI

RDY

#

//

B

_

A

1

5

B

_

CF

RA

M

E

#

//

B

_

A

2

3

B_

C

C

/BE2

#//B_A12

B_C

A

D

17//B_A24

B_C

A

D

18//B_A7

B_C

A

D

19//B_A25

B_

C

VS2

//B_

VS2

#

B_C

A

D

20//B_A6

B_

C

R

S

T

#

//B_R

ESET

B_C

A

D

21//B_A5

B_C

A

D

22//B_A4

B_

C

R

E

Q

#

//B_IN

PAC

K#

GN

D

B_C

A

D

23//B_A3

B_

C

C

/BE3

#//B_R

EG

#

B_C

A

D

24//B_A2

B_C

A

D

25//B_A1

B_C

A

D

26//B_A0

B_

C

VS1

//B_

VS1

#

B_

C

IN

T

#

//B_

R

EAD

Y(

IR

EQ

#

)

VC

C

B_

C

SER

R

#

//B_

W

AIT

#

B_

C

A

U

D

IO

//B_

BVD

2(

SPKR

#

)

B

_

CS

T

S

CHG

//

B

_

B

V

D

1

(S

T

S

CHG

#

/RI

#

)

B

_

CCL

K

RUN#

//

B

_

W

P

(I

O

IS

1

6

#

)

B

_

CCD2

#

//

B

_

CD2

#

B_C

A

D

27//B_D

0

B_C

A

D

28//B_D

8

B_C

A

D

29//B_D

1

B_C

A

D

30//B_D

9

B_

R

SVD

//B_D

2

NC

B_C

A

D

31//B_D

10

A_CCD1#//A_CD1#

A_CAD0//A_D3

A_CAD2//A_D11

A_CAD1//A_D4

A_CAD4//A_D12

A_CAD3//A_D5

A_CAD6//A_D13

A_CAD5//A_D6

VCC

A_RSVD//A_D14

A_CAD7//A_D7

A_CAD8//A_D15

GND

A_CC/BE0#//A_CE1#

A_CAD9//A_A10

A_CAD10//A_CE2#

A_CAD11//A_OE#

A_CAD12//A_A11

A_CAD13//A_IORD#

A_CAD15//A_IOWR#

A_CAD14//A_A9

A_CAD16//A_A17

A_C

A

D

31//A_D

10

A_R

SVD

//A_D

2

A

_

CA

D3

0

//

A

_

D

9

A

_

CA

D2

9

//

A

_

D

1

GN

D

A

_

CA

D2

8

//

A

_

D

8

A

_

CA

D2

7

//

A

_

D

0

A

_

CCD2

#

//

A

_

CD2

#

VC

C

A

_

CCL

K

RUN#

//

A

_

W

P

(I

O

IS

1

6

#

)

A

_

CS

T

S

CHG

//

A

_

B

V

D

1

(S

T

S

CHG

#

/RI

#

)

A_C

A

U

D

IO

//A_BVD

2

(SPKR

#)

A_

C

SER

R

#

//A_W

AIT

#

A_

C

IN

T

#//A_

R

EAD

Y(

IR

EQ#)

A_C

VS1

//A_

VS1#

A

_

CA

D2

6

//

A

_

A

0

A

_

CA

D2

5

//

A

_

A

1

A

_

CA

D2

4

//

A

_

A

2

VC

C

A_

C

C

/BE3

#//A_

R

EG#

A

_

CA

D2

3

//

A

_

A

3

A_

C

R

E

Q#

//A_IN

PAC

K#

A

_

CA

D2

2

//

A

_

A

4

VR

_

O

U

T

A

_

CA

D2

1

//

A

_

A

5

A_C

R

S

T

#

//A_R

ESET

A

_

CA

D2

0

//

A

_

A

6

A_C

VS2

//A_

VS2#

A_C

A

D

1

9//A_A25

A

_

CA

D1

8

//

A

_

A

7

A_C

A

D

1

7//A_A24

A_

C

C

/BE2

#//A_

A

12

A

_

CF

RA

M

E

#

//

A

_

A

2

3

VC

C

A_CIRDY#//A_A15

A_CTRDY#//A_A22

A_CCLK//A_A16

VCCA

A_CDEVSEL#//A_A21

A_CGNT#//A_WE#

A_CSTOP#//A_A20

GND

A_CPERR#//A_A14

A_CBLOCK#//A_A19

A_CPAR//A_A13

A_RSVD//A_A18

A_CC/BE1#//A_A8

A_A16

A_A22

B_D7

B_D7

B_A16

B_

R

E

G#

C3

.1uF

B_WE#

A_R

E

G

#

A_WE#

A_A23

A

_

CD2

#

BVCC

A_D

1

A_A9

B_D4

A_A22

B_

A24

B_A10

B_OE#

B_D1

B_CE2#

A_A20

B_

A15

B_D10

A_A18

B_A14

B_D0

A_WE#

A_A7

B_D14

B_A17

B_WE#

A_D6

B_A15

A_D14

A_D2

A_A17

3.3VCC

B_CD2#

B_D12

B_D15

B_A18

B_A18

B_A3

A_D0

B_D8

R1

47

AVPP

B_D5

A_A25

C8

.1uF

A_CE1#

B_A19

B_

A3

A_IN

PAC

K#

B_

D

1

0

A_D11

A_R

ESET

A_A12

A_CD1#

BVPP

A_A16

A_IORD#

C6

.1uF

A_D12

A_A10

B_

D

0

B_CD1#

B_IOWR#

A_D10

A_A14

A_D1

B_D11

B_

A4

A_D12

A_CE2#

B_BVD2

B_

A2

B_A10

A_A24

B_A2

B_A6

B_INPACK#

A_INPACK#

A_A21

B_D11

A_BVD2

A_A18

A_WP

B_D15

B_REG#

A_A1

B_IORD#

B_A21

A_A4

B_A24

A_A9

B_D6

A_A13

B_A17

A_A0

C4

.1uF

B_VS1#

B_

D

2

A_A12

C2

.1uF

B_A13

B_A13

B_OE#

B_D4

A_A3

A_D4

A_A5

B_

BVD

2

B_A14

A_A11

C1

1uF

A_IOWR#

A_OE#

A_D14

B_A9

A_CE2#

B_A21

A_D

1

0

B_D3

A_A23

A_VS1#

B_A19

B_A8

A_D15

B_RESET

A_A14

A_A11

B_BVD1

A_A4

A_A10

B_

A0

A_BVD

1

A_BVD

2

A_D13

B_

A5

B_CD1#

A_D3

A_A8

B_D14

B_

VS2#

P1

C-1318619_R2 (CB Connector)

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

GND

GND

B_CD1

B_D3

B_D11

B_D4

B_D12

B_D5

GND

B_D13

B_D6

B_D14

B_D7

B_D15

B_CE1

B_CE2

GND

B_A10

B_VS1

B_OE

B_IORD

B_A11

B_IOWR

B_A9

GND

B_A17

B_A8

B_A18

B_A13

B_A19

B_A14

B_A20

GND

B_WE

B_A21

B_READY/IREQ

B_VCC

B_NC

B_VPP

B_A16

B_A22

B_A15

GND

B_A23

B_A12

B_A24

B_A7

B_A25

B_A6

B_VS2

GND

B_A5

B_RESET

B_A4

B_WAIT

B_A3

B_INPACK

B_A2

GND

B_REG

B_A1

B_BVD2/SPKR

B_A0

B_BVD1/STSCHG

B_D0

B_D8

GND

B_D1

B_D9

B_D2

B_D10

B_WP/IOIS16

B_CD2

GND

GND

GND

GND

A_CD1

A_D3

A_D11

A_D4

A_D12

A_D5

GND

A_D13

A_D6

A_D14

A_D7

A_D15

A_CE1

A_CE2

GND

A_A10

A_VS1

A_OE

A_IORD

A_A11

A_IOWR

A_A9

GND

A_A17

A_A8

A_A18

A_A13

A_A19

A_A14

A_A20

GND

A_WE

A_A21

A_READY/IREQ

A_VCC

A_NC

A_VPP

A_A16

A_A22

A_A15

GND

A_A23

A_A12

A_A24

A_A7

A_A25

A_A6

A_VS2

GND

A_A5

A_RESET

A_A4

A_WAIT

A_A3

A_INPACK

A-A2

GND

A_REG

A_A1

A_BVD2/SPKR

A_A0

A_BVD1/STSCHG

A_D0

A_D8

GND

A_D1

A_D9

A_D2

A_D10

A_WP/IOIS16

A_CD2

GND

GND

B_A5

A_CE1#

B_

W

A

IT

#

B_

A22

B_A16

B_

W

P

B_

A7

B_A0

B_A22

A_D8

BVCC

B_D12

AVCC

B_A25

A_A7

A_IORD#

B_VS2#

C7

.1uF

A_W

P

R3

47

A_READY

B_

A6

B_CE1#

B_A8