6 digital audio interface (j60), J60), Description – Texas Instruments TAS5518 User Manual

Page 16

www.ti.com

2.6

Digital Audio Interface (J60)

Digital Audio Interface (J60)

The digital audio interface contains digital audio signal data (I

2

S), clocks, etc. Please refer to the TAS5518

Data Manual for signal timing and details not covered in this document.

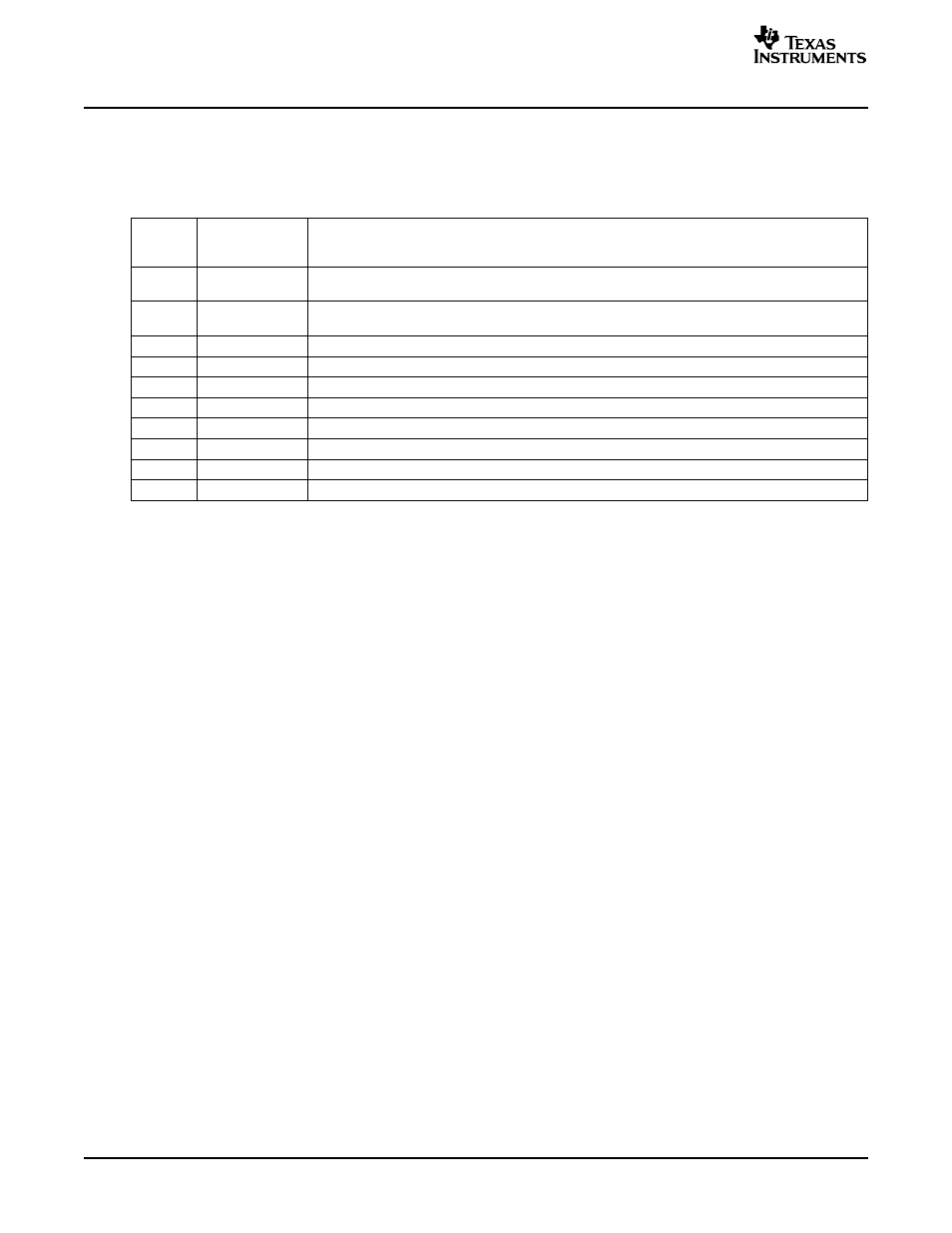

Table 2-8. J60 Pin Description

NET NAME

PIN

AT

DESCRIPTION

NO.

SCHEMATICS

1, 3, 10,

GND

Ground

12, 14, 16

Master clock input. Low-jitter system clock for PWM generation and reclocking. Ground connection

2

MCLK

from source to the TAS5518 must be a low-impedance connection.

3

GND

Ground

4

SDIN1

I

2

S data 1, channel 1 and 2

5

SDIN2

I

2

S data 2, channel 3 and 4

6

SDIN3

I

2

S data 3, channel 5 and 6

7

SDIN4

I

2

S data 4, channel 7 and 8

8, 9, 15

—

Reserved

11

SCLK

I

2

S bit clock

13

LRCLK

I

2

S left-right clock

System Interfaces

16

SLEU074 – June 2006

- THS4151 (26 pages)

- TRF1500 (74 pages)

- SLOU082 (28 pages)

- TAS5508-5121K8EVM (24 pages)

- TPA6102A2 (16 pages)

- TPA3001D1EVM (22 pages)

- TPA6030A4 (25 pages)

- TPA701 (26 pages)

- TPA6110A2 MSOP (18 pages)

- TAS5727 (21 pages)

- THS4503EVM (28 pages)

- TPA005D02 (50 pages)

- SLOU121 (42 pages)

- TPA0243 (20 pages)

- TPA0253 (20 pages)

- TPA102 MSOP (26 pages)

- THS4131 (26 pages)

- SLOU020A (28 pages)

- TPA751 MSOP (20 pages)

- TPA005D12 (44 pages)

- TPA6139A2 EVM (8 pages)

- TPA0103 (32 pages)

- SLOU106 (26 pages)

- THS4141 (26 pages)

- THS3001 (20 pages)

- TPA0233 (20 pages)

- TPA2008D2 (26 pages)

- 2004 (20 pages)

- TPA3003D2 (36 pages)

- SLAU081 (44 pages)

- TPA301 (28 pages)

- TPA3100D2 (11 pages)

- SLOU023A (26 pages)

- TAS5110D6REF (45 pages)

- TA5704EVM (27 pages)

- APA100 (42 pages)

- TPA3200D1 (30 pages)

- TAS5066PAG (22 pages)

- TPA6204A1 (16 pages)

- THS4150 (26 pages)

- TPA311 (28 pages)

- TPA3008D2 (31 pages)

- TPA6101A2 (16 pages)