Cores – Texas Instruments MICROPROCESSOR TI SITARA User Manual

Page 7

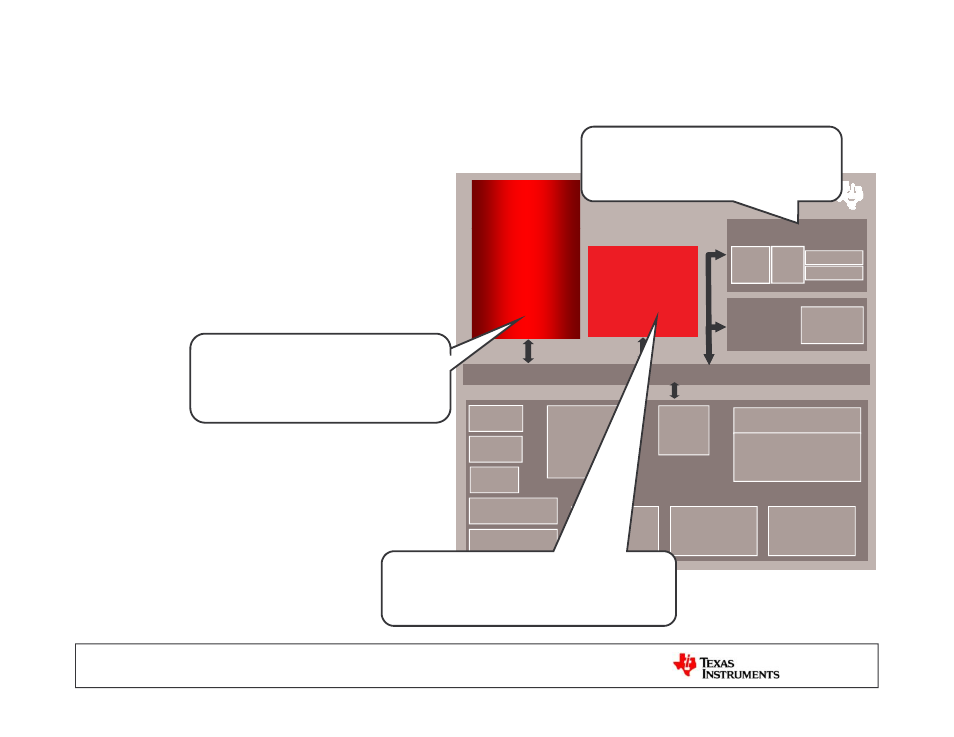

AM3517/05 Core and Accelerators

ARM

®

AM3517/05

processors

Display Subsystem

Cores

Multi window overlay system and

resizing for hardware accelerated

user interfaces

ARM

®

Cortex

™

-

A8

3D

Graphics

Accelerator

(3517)

Display Subsystem

10 bit DAC

10 bit DAC

LCD

Cont-

roller

Video

Enc

16-bit Video

Video

Processing

Cores

600 MHz Cortex A-8 with NEON™

coprocessor

PowerVR SGX 3D graphics

Accelerator – up to 10M

polygons / second

L3/L4 Interconnect

16-bit Video

Input

Processing

Front End

USB HS Host x2

Timers

HDQ /

CAN

polygons / second

Up to 1000 Dhrystone MIPS:

• OS’s like Linux or WinCE

• Excellent web experience

I2C x3

USB HS Host x2

McBSP x5

Timers

GP x12

WDT x1

HDQ /

1-wire

USB OTG

w/PHY

EMAC

CAN

Memory

ARM:

16 kB I-Cache; 16 kB D-Cache;

MMC/SD/

SDIO x3

DDR2

GPMC

McBSP x5

UARTx3

+1 w/IrDA

McSPI x4

16 kB I-Cache; 16 kB D-Cache;

256kB L2 Cache

On chip: 64kB SRAM; 128kB

ROM

DDR2 interface

GPMC: NAND/NOR I/F

• Up to 10M polygons per second

• Hardware based on screen display

• Easily create robust GUI’s

GPMC: NAND/NOR I/F

• Easily create robust GUI’s

7