Universal parallel port (upp am18x only), Streamline data i/o simple i/o protocol, And dacs – Texas Instruments MICROPROCESSOR TI SITARA User Manual

Page 23

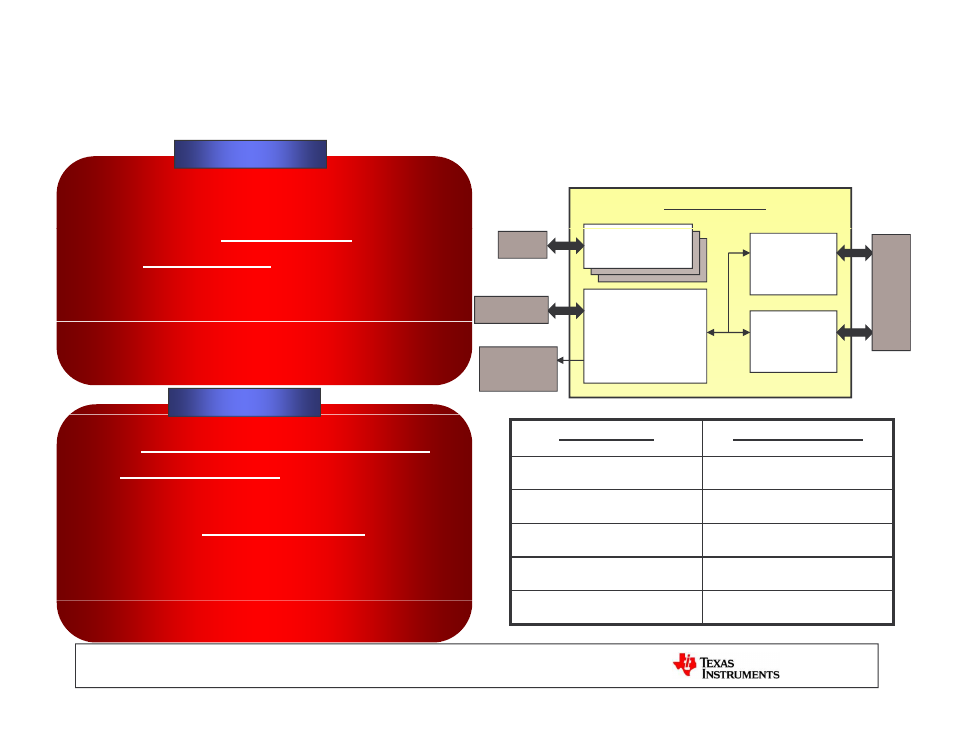

Universal Parallel Port (uPP AM18x only)

Config

uPP Peripheral

High Speed parallel data port

Two Bidirectional and

What Is uPP?

Config

Registers

I/O

Channel

A

I/O

Internal

E

xte

rn

al

P

in

s

CPU

Memory

Two Bidirectional and

Independent 16bit channels

Internal dedicated DMA to

streamline data I/O

I/O

Channel

B

Internal

DMA

E

xte

rn

al

P

in

s

CPU

Interrupt

streamline data I/O

Simple I/O Protocol

Value of uPP

Configuration

Throughput (MB/s)

1 Ch, 16-bit

120

2 Ch, 1 Way, 8-bit

120

Efficient Processor to FPGA

communication enabled by high

speed data I/O

2 Ch, 1 Way, 8-bit

120

2 Ch, 1 Way, 16-bit

160

2 Ch, 2 Way, 16-bit

240

HPI (16-bit)

50

Enable multi-processor system

design in various topologies

Interface with high speed ADCs

and DACs

HPI (16-bit)

50

and DACs

23