Electrical characteristics – Texas Instruments TPS54810 User Manual

Page 3

TPS54810

SLVS420B − MARCH 2002 − R EVISED FEBRUARY 2005

www.ti.com

3

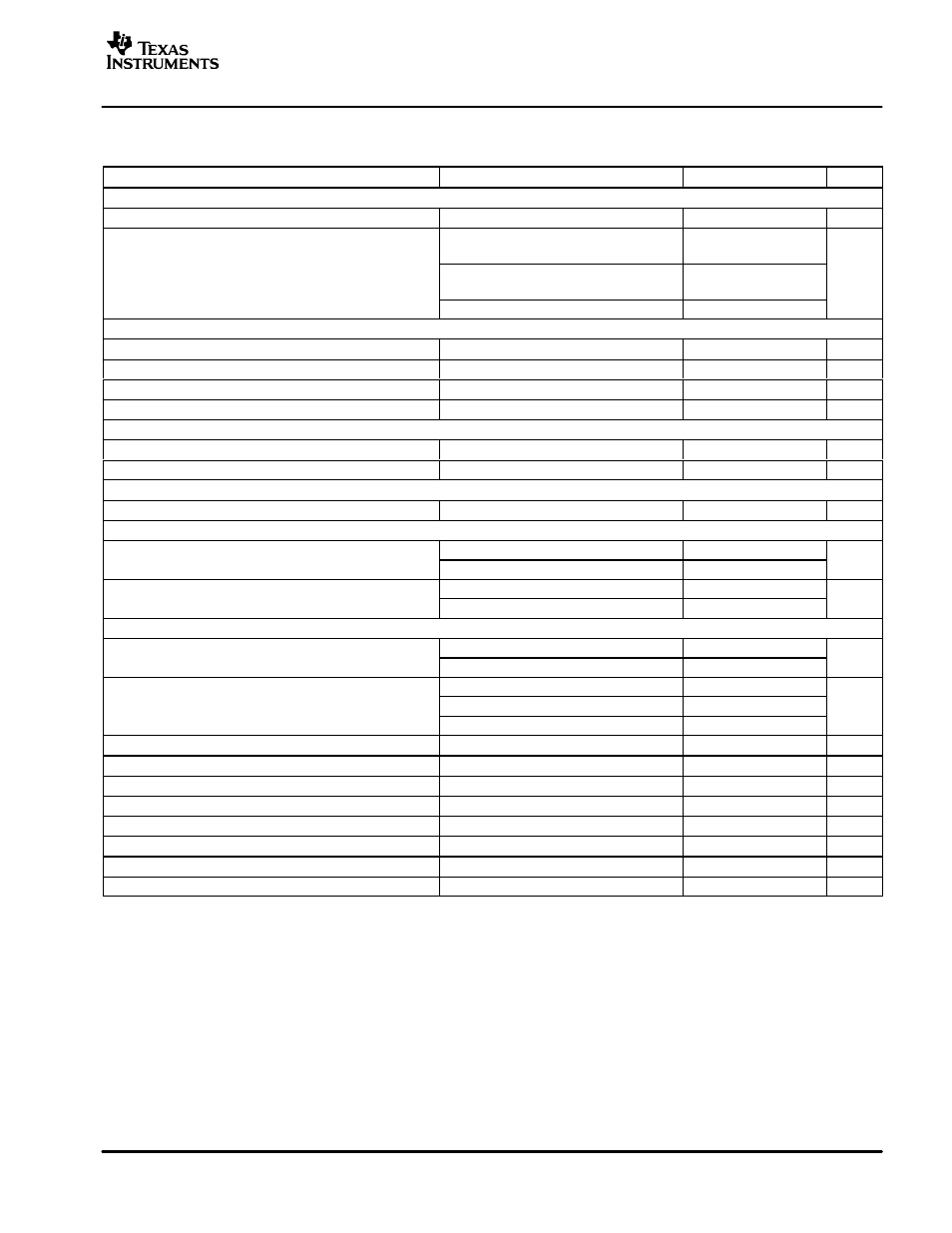

ELECTRICAL CHARACTERISTICS

T

J

= −40°C to 125°C, V

I

= 4 V to 6 V unless otherwise noted

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SUPPLY VOLTAGE, VIN

Input voltage range, VIN

4.0

6.0

V

f

s

= 350 kHz, SYNC ≤ 0.8 V, RT open,

PH pin open

11

15.8

I

(Q)

Quiescent current

f

s

= 550 kHz, SYNC ≥ 2.5 V, RT open,

PH pin open

16

23.5

mA

Shutdown, SS/ENA = 0 V

1.0

1.4

UNDER VOLTAGE LOCK OUT

Start threshold voltage, UVLO

3.8

3.85

V

Stop threshold voltage, UVLO

3.40

3.50

V

Hysteresis voltage, UVLO

0.14

0.16

V

Rising and falling edge deglitch, UVLO

(1)

2.5

µs

BIAS VOLTAGE

Output voltage, VBIAS

I

(VBIAS)

= 0

2.70

2.80

2.90

V

Output current, VBIAS

(2)

100

µA

CUMULATIVE REFERENCE

V

ref

Accuracy

0.882

0.891

0.900

V

REGULATION

Line regulation

(1) (3)

I

L

= 4 A, f

s

= 350 kHz, T

J

= 85°C

0.04

%/V

Line regulation

(1) (3)

I

L

= 4 A, f

s

= 550 kHz, T

J

= 85°C

0.04

%/V

Load regulation

(1) (3)

I

L

= 0 A to 8 A, f

s

= 350 kHz, T

J

= 85°C

0.03

%/A

Load regulation

(1) (3)

I

L

= 0 A to 8 A, f

s

= 550 kHz, T

J

= 85°C

0.03

%/A

OSCILLATOR

Internally set free running frequency range

SYNC ≤ 0.8 V, RT open

280

350

420

kHz

Internally set—free running frequency range

SYNC ≥ 2.5 V, RT open

440

550

660

kHz

RT = 180 kΩ (1% resistor to AGND)

252

280

308

Externally set—free running frequency range

RT = 100 kΩ (1% resistor to AGND)

460

500

540

kHz

Externally set free running frequency range

RT = 68 kΩ (1% resistor to AGND)

663

700

762

kHz

High level threshold, SYNC

2.5

V

Low level threshold, SYNC

0.8

V

Pulse duration, external sychronization, SYNC

(1)

50

ns

Frequency range, SYNC

(1)

330

700

kHz

Ramp valley

(1)

0.75

V

Ramp amplitude (peak-to-peak)

(1)

1

V

Minimum controllable on time

(1)

200

ns

Maximum duty cycle

(1)

90%

(1)

Specified by design

(2)

Static resistive loads only

(3)

Specified by the circuit used in Figure 9