Application headers – Renesas H8SX/1668R User Manual

Page 27

9.2. Application Headers

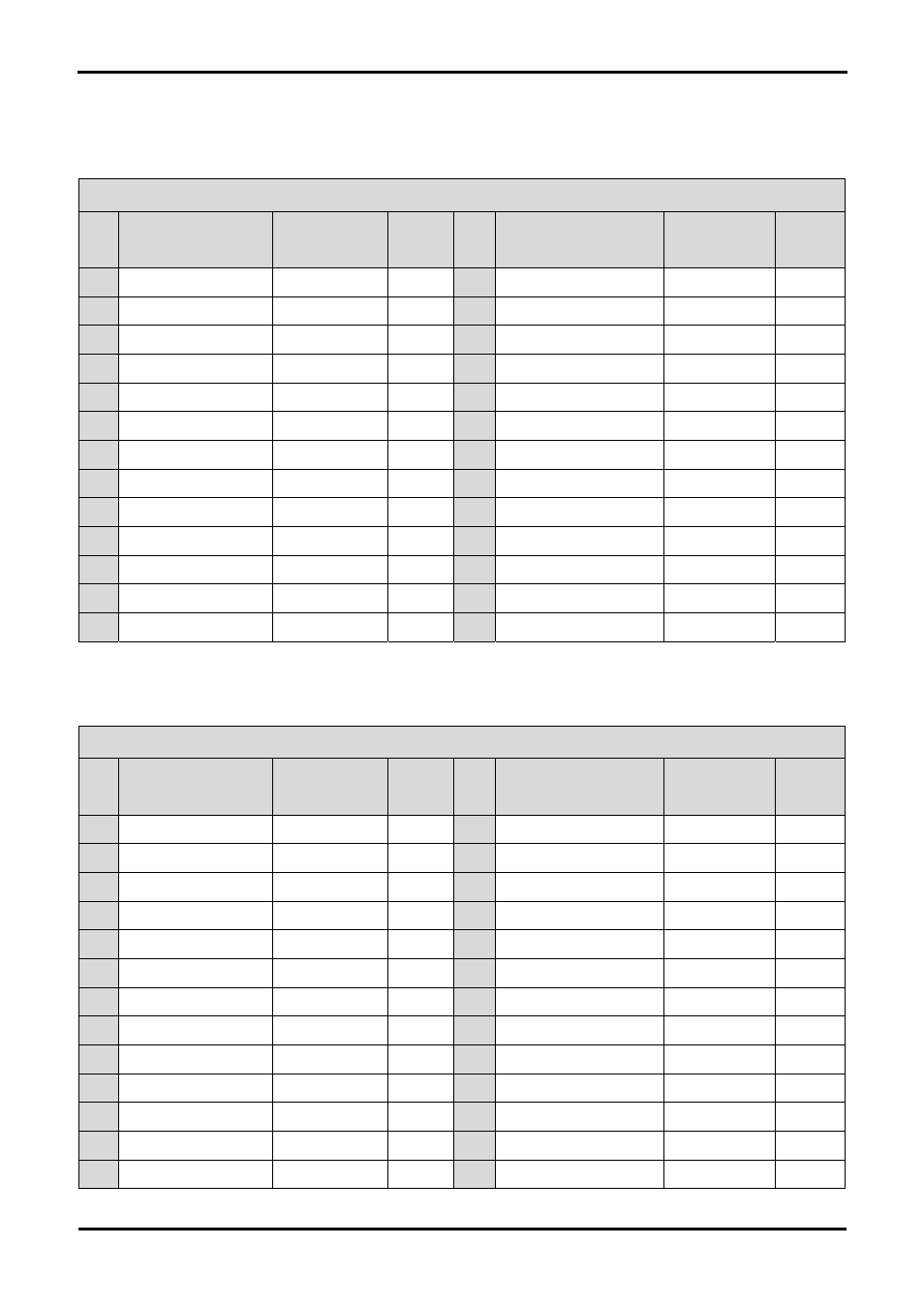

Table 9-5 to Table 9-9 below show the standard application header connections.

JA1

Pin Generic Header Name

CPU board

Signal Name

Device

Pin

Pin

Generic Header Name

CPU board

Signal Name

Device

Pin

1 5V

CON_5V

-

2 0V

GROUND

-

3 3V3

CON_3V3

-

4 0V

GROUND

-

5 AVCC

CON_AVCC 121 6 AVss

CON_AVSS 123

7 AVref

CON_VREF 125 8 ADTRG

ADTRGn

87

9 AD0

AN0

(**)

118 10 AD1

AN1

119

11 AD2

AN2

120

12 AD3

AN3

122

13 DAC0

DA0

(**)

127

14 DAC1

DA1

128

15 IO_0

IO0

(**)

49

16 IO_1

IO1

(**)

51

17 IO_2

IO2

(**)

52

18 IO_3

IO3

(**)

53

19 IO_4

IO4

(**)

54

20 IO_5

IO5

(**)

55

21 IO_6

IO6

59

22 IO_7

IO7

60

23 IRQ3

IRQ3n

(**)

87

24 IIC_EX

NC

-

25 IIC_SDA

SDA0

-

26 IIC_SCL

SCL0

-

Table 9-5: JA1 Standard Generic Header

JA2

Pin Generic Header Name

CPU board

Signal Name

Device

Pin

Pin

Generic Header Name

CPU board

Signal Name

Device

Pin

1 RESn

RESn

91

2 EXTAL

CON_EXTAL 97

3 NMIn

NMIn

61

4 VSS1

GROUND

-

5 WDT_OVF

WDTOVF

95

6 SCIaTX

TxD0

(**)

52

7 IRQ0

IRQ0n

84

8

SCIaRX RxD0

(**)

51

9 IRQ1

IRQ1n

85

10 SCIaCK

CLK0

(**)

49

11 UD

UD

(**)

53

12 CTSRTS

NC

-

13 Up

Up

(**)

105

14 Un

Un

(**)

106

15 Vp

Vp

(**)

56

16 Vn

Vn

(**)

57

17 Wp

Wp

(**)

55

18 Wn

Wn

(**)

54

19 TMR0

TIOCA0

(**)

56

20 TMR1

TIOCA2

(**) 105

21 TRIGa

TIOCB0

57

22 TRIGb

TIOCB2

(**) 106

23 IRQ2

IRQ3n

(**)

87

24 TRISTn

TRISTn

109

25 -

-

-

26 -

-

-

Table 9-6: JA2 Standard Generic Header

25