National Products DS90C3202 User Manual

Page 17

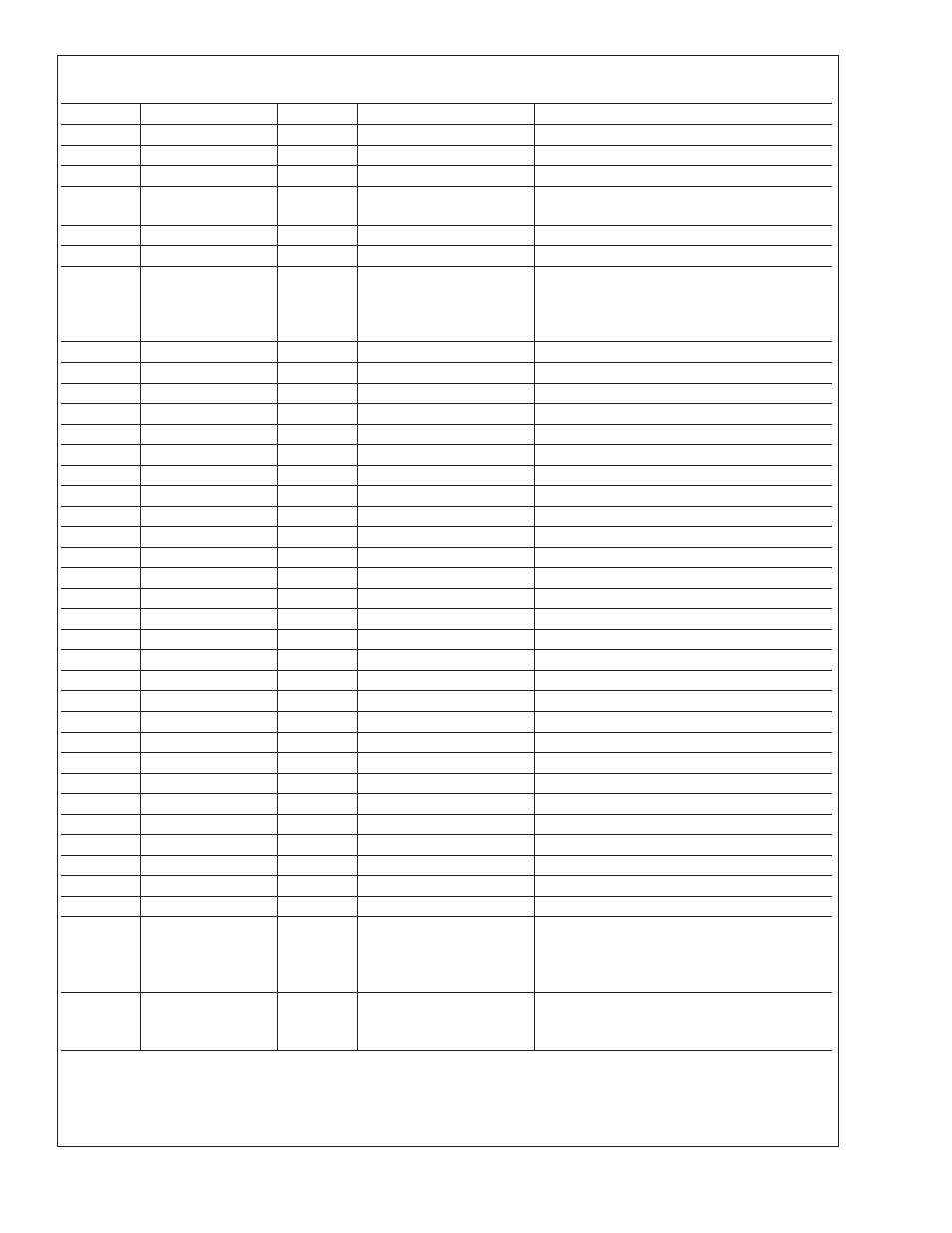

DS90C3202 Pin Descriptions

(Continued)

Pin No.

Pin Name

I/O

Pin Type

Description

92

RXOA4

O/P

LVTTL O/P

LVTTL level data output

93

RXOA5

O/P

LVTTL O/P

LVTTL level data output

94

RXOA6

O/P

LVTTL O/P

LVTTL level data output

95

VDD5

VDD

LVTTL O/P PWR

Power supply pin for LVTTL outputs and digital

circuitry

96

VSS5

GND

LVTTL O/P PWR

Ground pin for LVTTL outputs and digital circuitry

97

RESRVD

I/P

LVTTL I/P (pulldown)

Tie to VSS for correct functionality

98

MODE1

I/P

Digital (pulldown)

“ODD” Bank Enable

0 = LVTTL ODD OUTPUTS DISABLED

(Data Output Low)

1 = LVTTL ODD OUTPUTS ENABLED

99

VSSL

GND

LVDS PWR

Ground pin for LVDS

100

VDDL

VDD

LVDS PWR

Power supply pin for LVDS

101

RXOA-

I/P

LVDS I/P

Negative LVDS differential data input

102

RXOA+

I/P

LVDS I/P

Positive LVDS differential data input

103

RXOB-

I/P

LVDS I/P

Negative LVDS differential data input

104

RXOB+

I/P

LVDS I/P

Positive LVDS differential data input

105

RXOC-

I/P

LVDS I/P

Negative LVDS differential data input

106

RXOC+

I/P

LVDS I/P

Positive LVDS differential data input

107

RXOD-

I/P

LVDS I/P

Negative LVDS differential data input

108

RXOD+

I/P

LVDS I/P

Positive LVDS differential data input

109

RXOE-

I/P

LVDS I/P

Negative LVDS differential data input

110

RXOE+

I/P

LVDS I/P

Positive LVDS differential data input

111

VSSL

GND

LVDS PWR

Ground pin for LVDS

112

VSSL

GND

LVDS PWR

Ground pin for LVDS

113

VDDL

VDD

LVDS PWR

Power supply pin for LVDS

114

VDDL

VDD

LVDS PWR

Power supply pin for LVDS

115

RCLKIN-

I/P

LVDS I/P

Negative LVDS differential clock input

116

RCLKIN+

I/P

LVDS I/P

Positive LVDS differential clock input

117

RXEA-

I/P

LVDS I/P

Negative LVDS differential data input

118

RXEA+

I/P

LVDS I/P

Positive LVDS differential data input

119

RXEB-

I/P

LVDS I/P

Negative LVDS differential data input

120

RXEB+

I/P

LVDS I/P

Positive LVDS differential data input

121

RXEC-

I/P

LVDS I/P

Negative LVDS differential data input

122

RXEC+

I/P

LVDS I/P

Positive LVDS differential data input

123

RXED-

I/P

LVDS I/P

Negative LVDS differential data input

124

RXED+

I/P

LVDS I/P

Positive LVDS differential data input

125

RXEE-

I/P

LVDS I/P

Negative LVDS differential data input

126

RXEE+

I/P

LVDS I/P

Positive LVDS differential data input

127

MODE0

I/P

Digital (pulldown)

“EVEN” Bank Enable

0 = LVTTL EVEN OUTPUTS DISABLED

(Data Output Low)

1 = LVTTL EVEN OUTPUTS ENABLED

128

RFB

I/P

Digital (pulldown)

Rising Falling Bar (Figure 9)

0 = FALLING EDGE DATA STROBE

1 = RISING EDGE DATA STROBE

DS90C3202

www.national.com

17