Chapter 5 pin descriptions, Chapter 5, Pin descriptions – SMSC USB2250i User Manual

Page 11: Usb2250/50i/51/51i 128-pin vtqfp pin descriptions

Ultra Fast USB 2.0 Multi-Slot Flash Media Controller

Datasheet

SMSC USB2250/50i/51/51i

11

Revision 1.1 (05-29-08)

DATASHEET

Chapter 5 Pin Descriptions

This section provides a detailed description of each signal. The signals are arranged in functional

groups according to their associated interface.

The “n” symbol in the signal name indicates that the active, or asserted, state occurs when the signal

is at a low voltage level. When “n” is not present before the signal name, the signal is asserted at the

high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working

with a mixture of “active low” and “active high” signals. The term assert, or assertion, indicates that a

signal is active, independent of whether that level is represented by a high or low voltage. The term

negate, or negation, indicates that a signal is inactive.

5.1

USB2250/50i/51/51i 128-Pin VTQFP Pin Descriptions

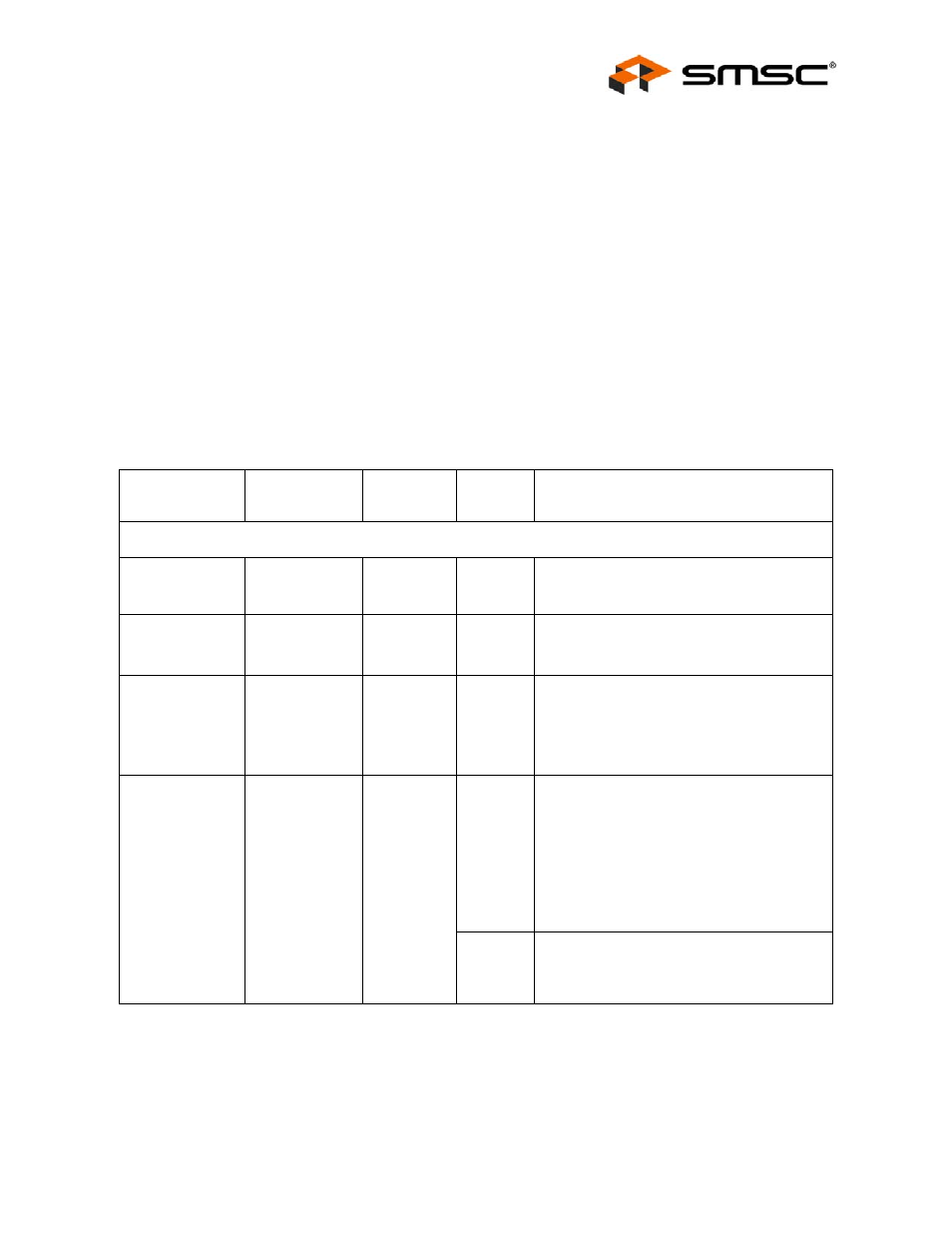

Table 5.1 USB2250/50i/51/51i 128-Pin VTQFP Pin Descriptions

NAME

SYMBOL

128-PIN

VTQFP

BUFFER

TYPE

DESCRIPTION

COMPACT FLASH INTERFACE

CF Chip Select 0

CF_nCS0

71

O12

This pin is the active low chip select 0 signal

for the task file registers of the CF ATA

device in True IDE mode.

CF Register

Address

CF_SA[2:0]

82

83

84

I/O12

These pins are the register select address

bits for the CF ATA device.

CF Interrupt

CF_IRQ

74

IPD

This is the active high interrupt request

signal from the CF device.

This pin has an internal weak pull-down

resistor that can be controlled by:

CF_INTF_EN bit of CFC_ATA_MODE_CTL.

CF Data 15-8 /

GPIO

CF_D[15:8] /

GPIO[31:24]

70

68

66

62

60

90

89

87

I/O12PD

CF_D[15:8]: The bi-directional data signals

CF_D15 - CF_D8 in True IDE mode data

transfer

In True IDE Mode, all task file register

operations occur on the CF_D[7:0], while

data transfer occurs on CF_D[15:0].

The bi-directional data signal has an internal

weak pull-down resistor.

I/O12

GPIO[31:24]: These pins are GPIOs if the

CF_INTF_EN bit of the CFC_ATA_MODE

CTL is disabled and the EXTENDED_GPIO

bit is set in UTIL_CONFIG1 is enabled.