Jtag/debug interface, Initialization interface, Miscellaneous signals – Sun Microsystems SME5224AUPA-400 User Manual

Page 36

8

SME5224AUPA-400

400 MHz CPU, 4.0 MB E-Cache

UltraSPARC

™

-II CPU Module

July 1999

Sun Microsystems, Inc

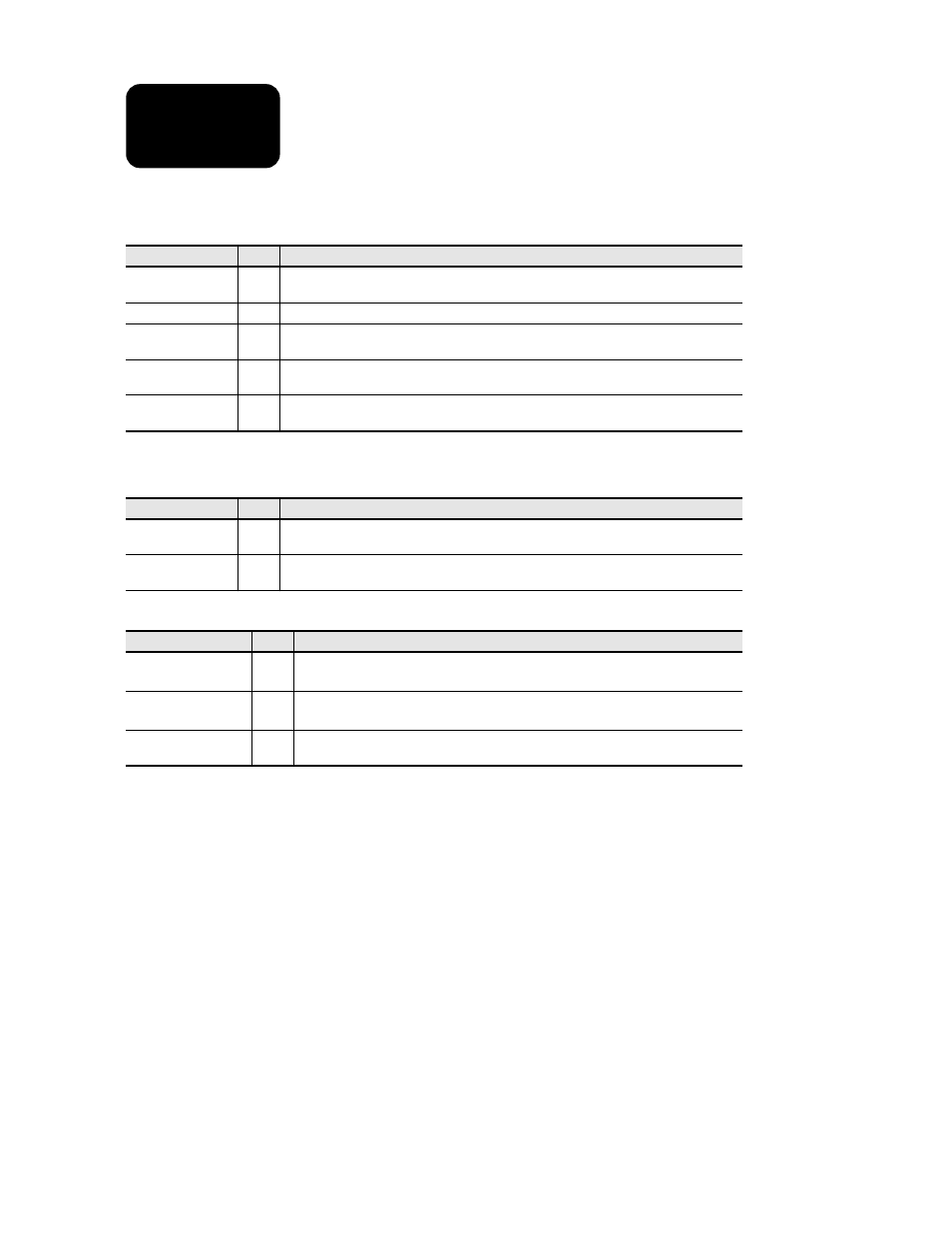

JTAG/Debug Interface

Signal

Type

Name and Function

TDO

O

IEEE 1149 test data output. A three-state signal driven only when the TAP controller is

in the shift-DR state.

TDI

I

IEEE 1149 test data input. This pin is internally pulled to logic one when not driven.

TCK

I

IEEE 1149 test clock input. This pin if not hooked to a clock source must always be

driven to a logic 1 or a logic 0.

TMS

I

IEEE 1149 test mode select input. This pin is internally pulled to logic one when not

driven. Active high.

TRST_L

I

IEEE 1149 test reset input (active low). This pin is internally pulled to logic one when not

driven. Active low.

Initialization Interface

Signal

Type

Name and Function

UPA_RESET_L

I

Driven by the system controller for the POR (power-on) resets and the fatal system

reset. Asserted asynchronously. Deasserted synchronous to UPA_CLK. Active low.

UPA_XIR_L

I

Driven to signal externally initiated reset (XIR). Actually acts like a non-maskable

interrupt. Synchronous to UPA_CLK. Active low, asserted for one clock cycle.

Miscellaneous Signals

Signal

Type

Name and Function

TEMP_SENSE_NEG

TEMP_SENSE_POS

O

Connected to a thermistor

[1]

adjacent to the CPU package.

1. The thermistor used on the module (SME5224AUPA-400) is manufactured by KOA. Operating at 47K the thermistor has KOA part

number NT32BT473J.

POWER_SET_POS

POWER_SET_NEG

O

POWER_SET_NEG is tied to GND on the module. POWER_SET_POS is connected

to GND via a 1690-ohm resistor. Sets voltage of programmable supply.

POWER_OV

O

Connected to GND via a 1180-ohm resistor. Sets overvoltage level for programmable

supply.