Datasheet – SMSC USB3290 User Manual

Page 33

Small Footprint Hi-Speed USB 2.0 Device PHY with UTMI Interface

Datasheet

SMSC USB3290

33

Revision 1.5 (11-02-07)

DATASHEET

Notes:

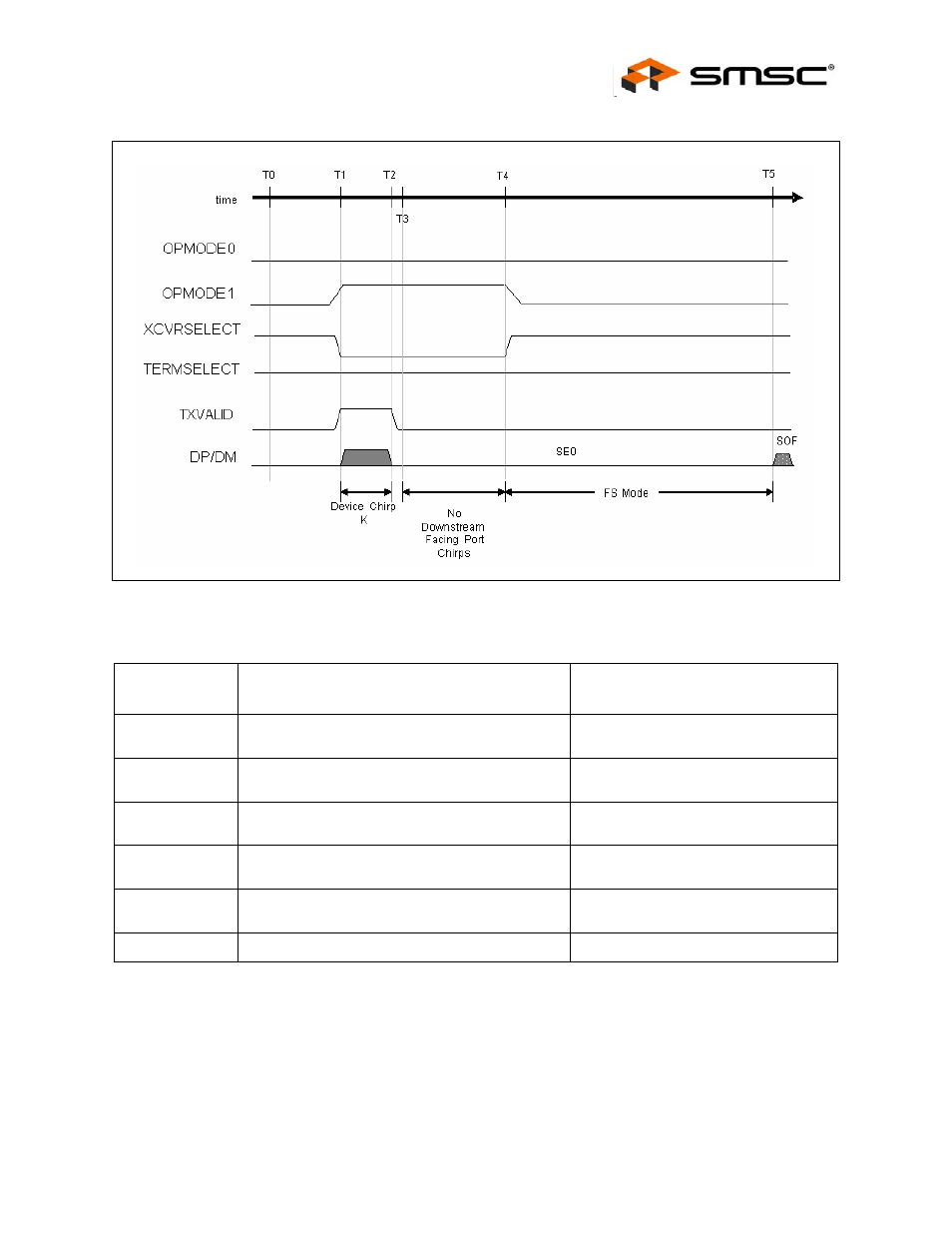

T0 may occur to 4ms after HS Reset T0.

The SIE must assert the Chirp K for 66000 CLKOUT cycles to ensure a 1ms minimum duration.

Figure 8.3 HS Detection Handshake Timing Behavior (FS Mode)

Table 8.6 HS Detection Handshake Timing Values (FS Mode)

TIMING

PARAMETER

DESCRIPTION

VALUE

T0

HS Handshake begins. DP pull-up enabled, HS

terminations disabled.

0 (reference)

T1

Device enables HS Transceiver and asserts Chirp

K on the bus.

T0 < T1 < HS Reset T0 + 6.0ms

T2

Device removes Chirp K from the bus. 1ms

minimum width.

T1 + 1.0 ms < T2 <

HS Reset T0 + 7.0ms

T3

Earliest time when downstream facing port may

assert Chirp KJ sequence on the bus.

T2 < T3 < T2+100µs

T4

Chirp not detected by the device. Device reverts to

FS default state and waits for end of reset.

T2 + 1.0ms < T4 <

T2 + 2.5ms

T5

Earliest time at which host port may end reset

HS Reset T0 + 10ms