Table 2 data interface pins, Product preview – SMSC USB3250 User Manual

Page 6

Hi-Speed USB Device Transceiver with UTMI Interface

Revision 1.7 (05-11-07)

6

SMSC USB3250

PRODUCT PREVIEW

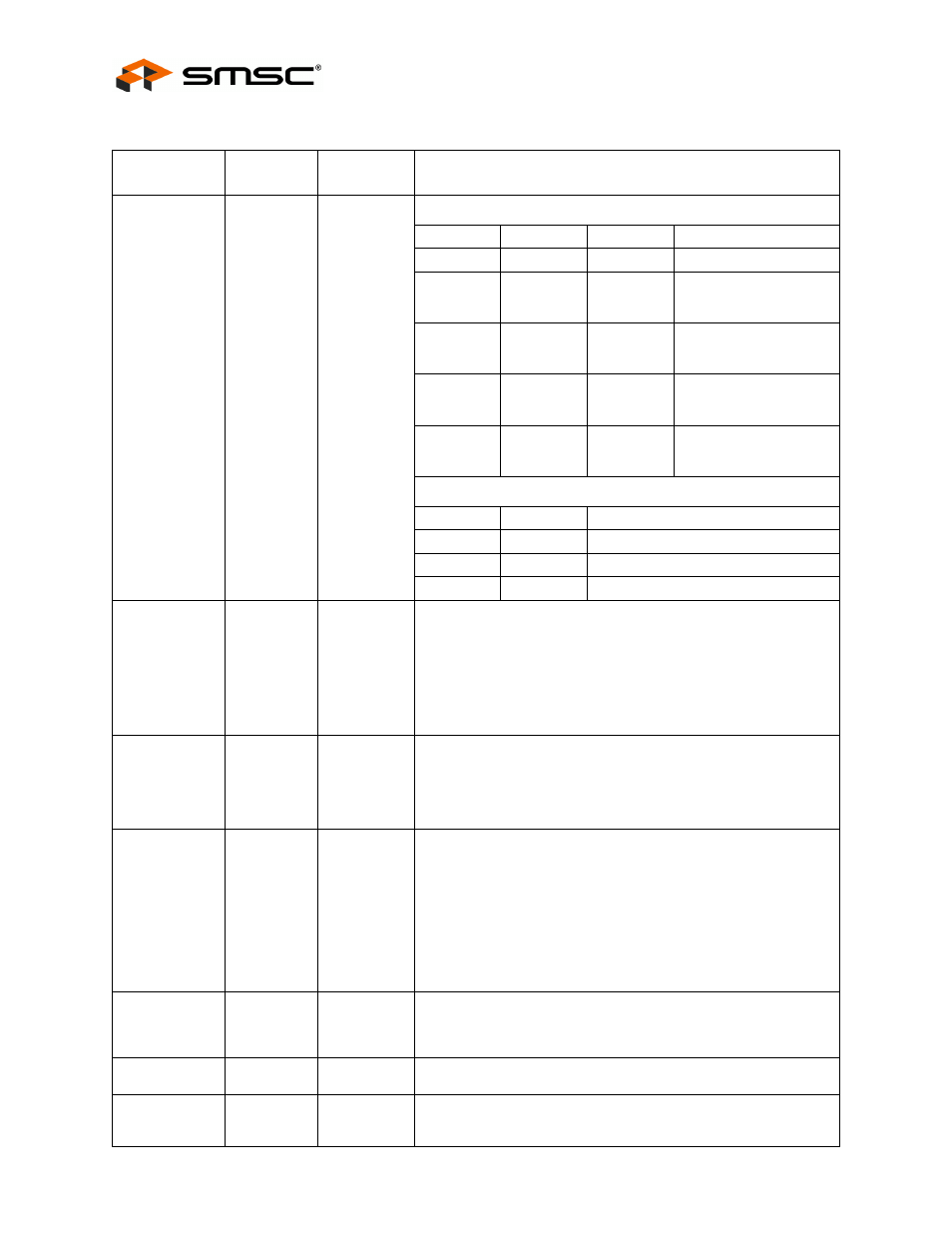

Table 2 Data Interface Pins

NAME

DIRECTION

ACTIVE

LEVEL

DESCRIPTION

DATA[15:0]

Bidir

N/A

DATA BUS. 16-BIT BIDIRECTIONAL MODE.

TXVALID

RXVALID

VALIDH

DATA[15:0]

0

0

X

Not used

0

1

0

DATA[7:0] output is valid

for receive

VALIDH is an output

0

1

1

DATA[15:0] output is

valid for receive

VALIDH is an output

1

X

0

DATA[7:0] input is valid

for transmit

VALIDH is an input

1

X

1

DATA[15:0] input is valid

for transmit

VALIDH is an input

DATA BUS. 8-BIT UNIDIRECTIONAL MODE.

TXVALID

RXVALID

DATA[15:0]

0

0

Not used

0

1

DATA[15:8] output is valid for receive

1

X

DATA[7:0] input is valid for transmit

TXVALID

Input

High

Transmit Valid. Indicates that the TXDATA bus is valid for

transmit. The assertion of TXVALID initiates the transmission of

SYNC on the USB bus. The negation of TXVALID initiates EOP

on the USB.

Control inputs (OPMODE[1:0], TERMSELECT,XCVRSELECT)

must not be changed on the de-assertion or assertion of TXVALID.

The PHY must be in a quiescent state when these inputs are

changed.

TXREADY

Output

High

Transmit Data Ready. If TXVALID is asserted, the SIE must

always have data available for clocking into the TX Holding

Register on the rising edge of CLKOUT. TXREADY is an

acknowledgement to the SIE that the transceiver has clocked the

data from the bus and is ready for the next transfer on the bus. If

TXVALID is negated, TXREADY can be ignored by the SIE.

VALIDH

Bidir

N/A

Transmit/Receive High Data Bit Valid (used in 16-bit mode

only). When TXVALID = 1, the 16-bit data bus direction is

changed to inputs, and VALIDH is an input. If VALIDH is asserted,

DATA[15:0] is valid for transmission. If deasserted, only DATA[7:0]

is valid for transmission. The DATA bus is driven by the SIE.

When TXVALID = 0 and RXVALID = 1, the 16-bit data bus

direction is changed to outputs, and VALIDH is an output. If

VALIDH is asserted, the DATA[15:0] outputs are valid for receive.

If deasserted, only DATA[7:0] is valid for receive. The DATA bus

is read by the SIE.

RXVALID

Output

High

Receive Data Valid. Indicates that the RXDATA bus has received

valid data. The Receive Data Holding Register is full and ready to

be unloaded. The SIE is expected to latch the RXDATA bus on the

rising edge of CLKOUT.

RXACTIVE

Output

High

Receive Active. Indicates that the receive state machine has

detected Start of Packet and is active.

RXERROR

Output

High

Receive Error. 0: Indicates no error. 1: Indicates a receive error

has been detected. This output is clocked with the same timing as

the RXDATA lines and can occur at anytime during a transfer.