5 interrupt status & control register (base + 1c) – Intel cPCI-7200 User Manual

Page 32

24

• Register Format

O_TRG

: Digital Output Trigger Signal

This bit is used to control the O_TRG output of PCI-7200; the signal is

on CN1 pin 36 of PCI-7200, CN1 pin 26 of cPCI-7200, CN2 pin 34 of

LPCI 7200S when

1: O_TRG 1 goes High (1)

0: O_TRG 1 goes Low (0)

Digital I/O FIFO Status:

I_OVR

: Input data overrun

1: Digital Input FIFO is full (overrun) during input data transfer

0: No input data overrun occurred

Input data overrun occurred, the I_OVR bit is set when input FIFO is

full and there is new input data coming in. This bit can be cleared by

writing “1” to it.

O_UND

: Output data FIFO is underrun

1: Output FIFO is empty during output data transfer

0: No output data underrun occurred

Output data underrun, the O_UND bit is set when output FIFO is

empty and the output request for new data, this bit can be cleared by

writing “1” to it.

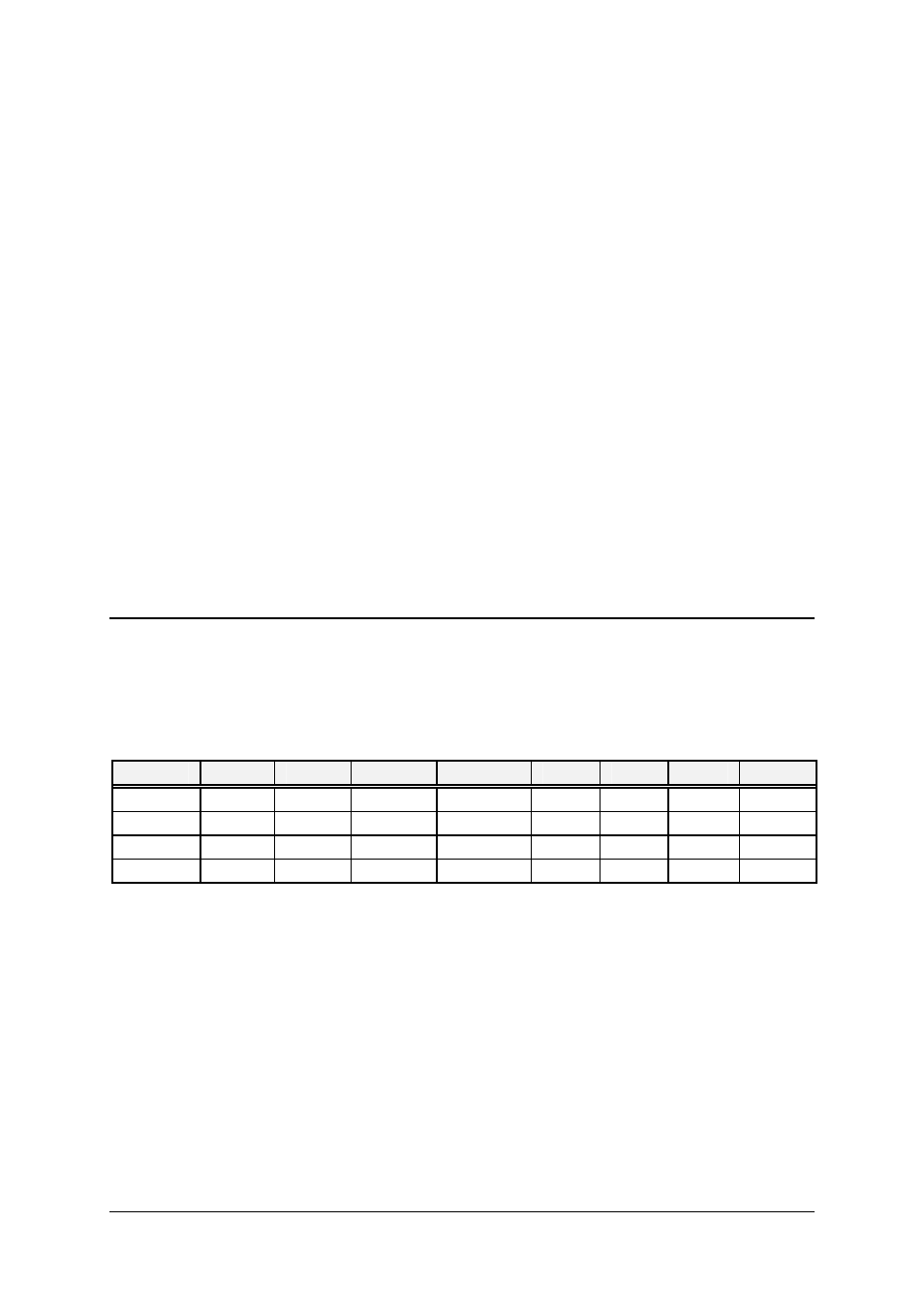

3.5 Interrupt Status & Control Register (BASE + 1C)

The interrupt mode/status is set/checked through this register.

Address: BASE + 1C

Attribute: READ/WRITE

Data Format:

Byte

7

6

5

4

3

2

1

0

Base

+1C SI_TO SI_REQ SO_ACK T2_EN

T1_EN T0_EN II_REQ IO_ACK

Base

+1D FIFOFF FIFOEF FIFORST REQ_NEG T1_T2 T0_T2 SI_T2 SI_T1

Base

+1E

---- ---- ---- ----

---- ---- ---- ----

Base

+1F

---- ---- ---- ----

---- ---- ---- ----

Interrupt Control:

With the PCI-7200, interrupts can be triggered by many signal sources such as

O_ACK, I_REQ, timer 0, timer 1, and timer 2. The following bits control the

interrupt source:

IO_ACK:

Interrupt is triggered by O_ACK signal.

1: O_ACK interrupt is enabled

0: O_ACK interrupt is disabled

II_REQ:

Interrupt is triggered by I_REQ signal.

1: I_REQ interrupt is enabled

0: I_REQ interrupt is disabled