Typical operating characteristics (continued) – Maxim Integrated MAX12527 User Manual

Page 10

MAX12527

Dual, 65Msps, 12-Bit, IF/Baseband ADC

10

______________________________________________________________________________________

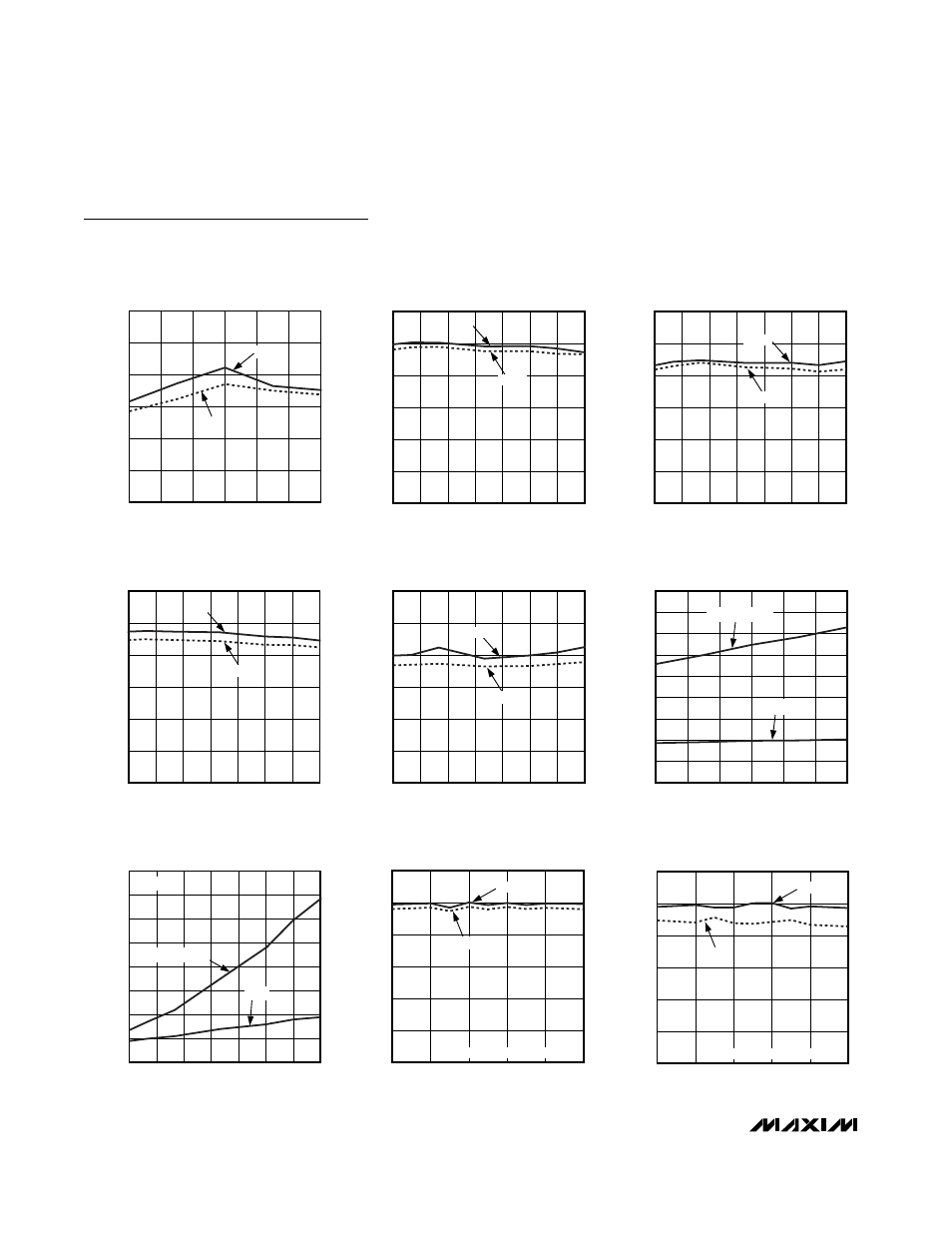

-THD, SFDR vs. ANALOG SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 175MHz)

MAX12527 toc22

V

DD

(V)

-THD, SFDR (dBc)

3.5

3.4

3.3

3.2

3.1

65

70

75

80

85

90

60

3.0

3.6

-THD

SFDR

SNR, SINAD vs. DIGITAL SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 70MHz)

MAX12527 toc23

OV

DD

(V)

SNR, SINAD (dB)

3.3

3.0

2.7

2.4

2.1

1.8

62

64

66

68

70

72

60

1.5

3.6

SNR

SINAD

-THD, SFDR vs. DIGITAL SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 70MHz)

MAX12527 toc24

OV

DD

(V)

-THD, SFDR (dBc)

3.3

3.0

2.7

2.4

2.1

1.8

65

70

75

80

85

90

60

1.5

3.6

-THD

SFDR

SNR, SINAD vs. DIGITAL SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 175MHz)

MAX12527 toc25

OV

DD

(V)

SNR, SINAD (dB)

3.3

3.0

2.7

2.4

2.1

1.8

62

64

66

68

70

72

60

1.5

3.6

SNR

SINAD

-THD, SFDR vs. DIGITAL SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 175MHz)

MAX12527 toc26

OV

DD

(V)

-THD, SFDR (dBc)

3.3

3.0

2.7

2.4

2.1

1.8

65

70

75

80

85

90

60

1.5

3.6

-THD

SFDR

P

DISS

, I

VDD

(ANALOG) vs. ANALOG SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 175MHz)

MAX12527 toc27

V

DD

(V)

P

DISS

, I

VDD

(mW, mA)

3.5

3.4

3.3

3.2

3.1

100

200

300

400

500

600

700

800

900

0

3.0

3.6

P

DISS

(ANALOG)

I

VDD

P

DISS

, I

OVDD

(DIGITAL) vs. DIGITAL SUPPLY VOLTAGE

(f

CLK

= 65.00352MHz, f

IN

= 175MHz)

MAX12527 toc28

OV

DD

(V)

P

DISS

, I

OVDD

(mW, mA)

3.3

3.0

1.8

2.1

2.4

2.7

10

20

30

40

50

60

70

80

0

1.5

3.6

P

DISS

(DIGITAL)

C

L

≈ 5pF

I

OVDD

SNR, SINAD vs. CLOCK DUTY CYCLE

(f

IN

= 70MHz, A

IN

= -0.5dBFS)

MAX12527 toc29

CLOCK DUTY CYCLE (%)

SNR, SINAD (dB)

65

55

45

35

62

64

66

68

70

72

60

25

75

SNR

SINAD

SINGLE-ENDED CLOCK INPUT DRIVE

-THD, SFDR vs. CLOCK DUTY CYCLE

(f

IN

= 70MHz, A

IN

= -0.5dBFS)

MAX12527 toc30

CLOCK DUTY CYCLE (%)

-THD, SFDR (dBc)

65

55

45

35

65

70

75

80

85

90

60

25

75

-THD

SFDR

SINGLE-ENDED CLOCK INPUT DRIVE

Typical Operating Characteristics (continued)

(V

DD

= 3.3V, OV

DD

= 2.0V, GND = 0, REFIN = REFOUT (internal reference mode), C

L

≈ 5pF at digital outputs, V

IN

= -0.5dBFS,

DIFFCLK/SECLK = OV

DD

, PD = GND, G/T = GND, f

CLK

= 65MHz (50% duty cycle), T

A

= +25°C, unless otherwise noted.)