Serial data input timing, Mb15e07sl – FUJITSU MB15E07SL User Manual

Page 13

MB15E07SL

13

■

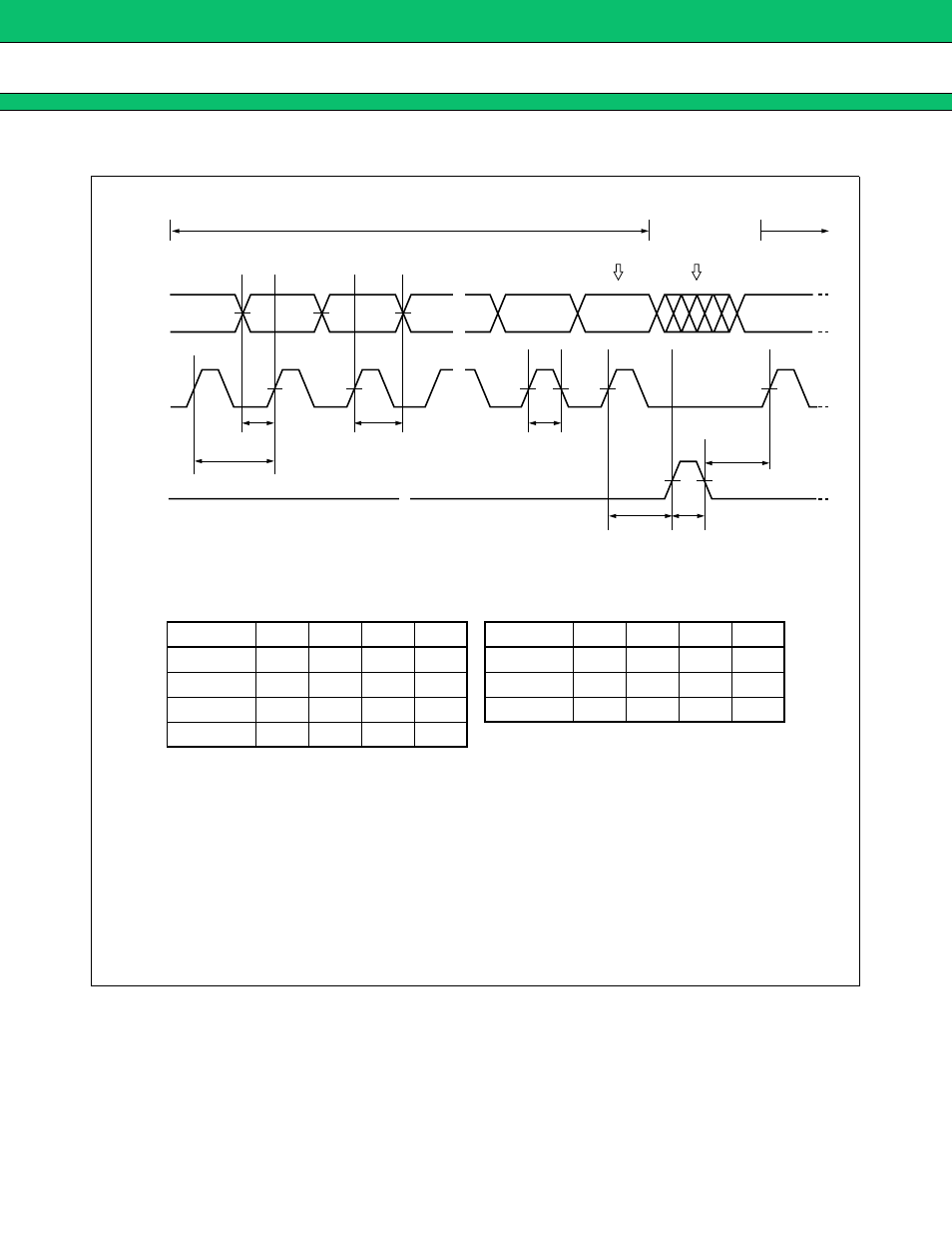

SERIAL DATA INPUT TIMING

1st data

2nd data

Control bit

Invalid data

Data

Clock

LE

MSB

LSB

t

1

t

2

t

3

t

6

t

5

t

4

t

7

∼

∼

∼

∼

Note : LE should be “L” when the data is transferred into the shift register.

Parameter

Min

Typ

Max

Unit

t

1

20

–

–

ns

t

2

20

–

–

ns

t

3

30

–

–

ns

t

4

30

–

–

ns

Parameter

Min

Typ

Max

Unit

t

5

100

–

–

ns

t

6

20

–

–

ns

t

7

100

–

–

ns

On the rising edge of the clock, one bit of data is transferred into the shift register.