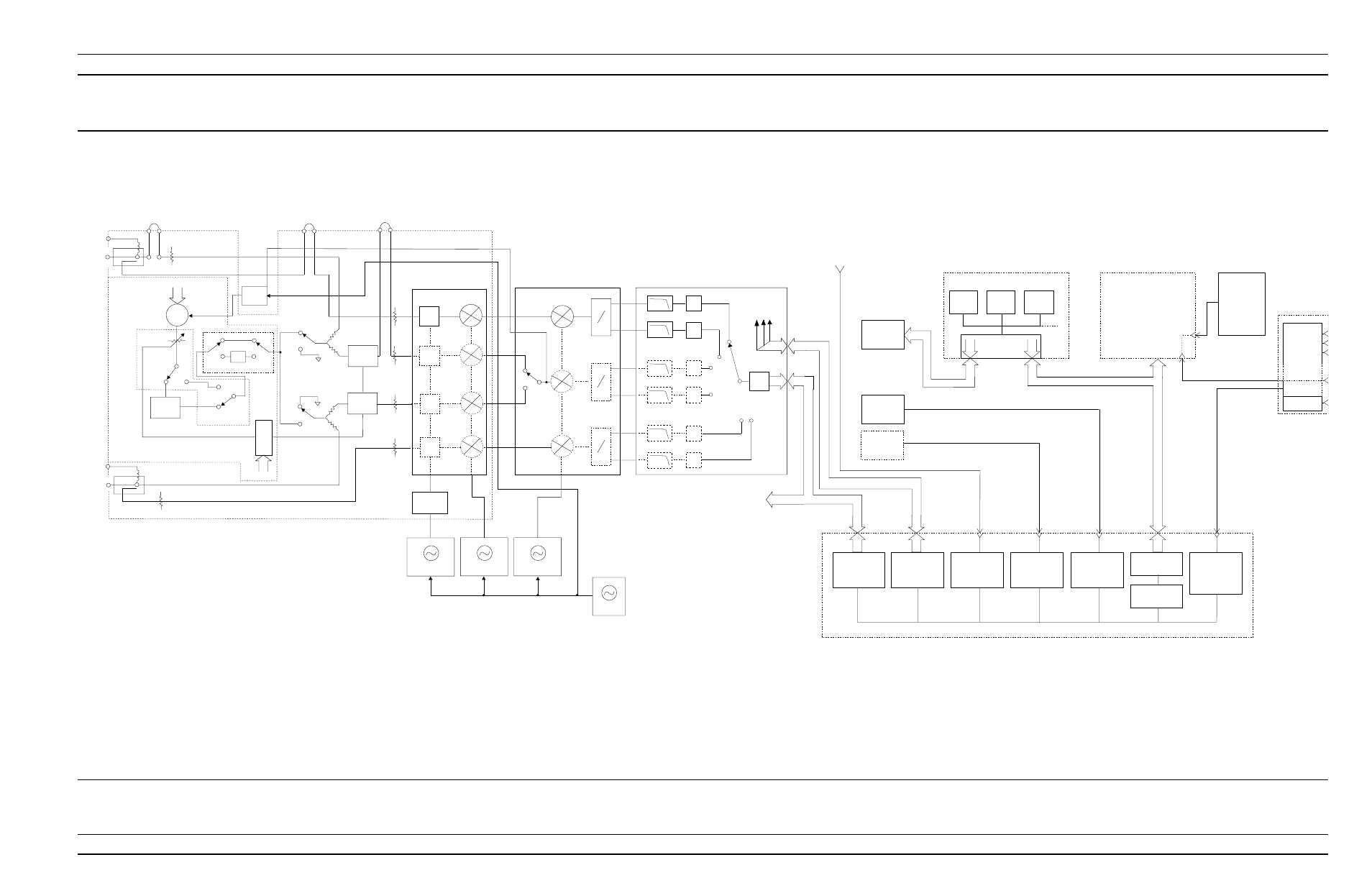

System description system overview, Figure 7-1 – Anritsu 373XXA User Manual

Page 100

373XXA MM

7-5

SYSTEM DESCRIPTION

SYSTEM OVERVIEW

A/D

S/H

S/H

ANALOG

MUX

S/H

S/H

S/H

CTL

EXTERNAL

KEYBOARD

A/D BUS

QUIET BUS

VME

INTERFACE

TO ANALOG PCB'S

(CTL & DATA)

S/H

S

S

S

D

D

D

YIG

PORT 1

PORT 2

bias tee

bias tee

* pad values:

a channels

b channels

37347B and below

20dB

6db

37369B

6dB

3db

SDM

LOCK

DET

QUAD

SAMPLER/BUFFER

IF / SYNC/ DET

FLTR / S/H / A/D

2X

F

LVL

DET

LVL

DET

F

R

R

0-40dB

Step Attenuator

ALC

SWITCHED

FILTER

DOWN

CONV

SIGNAL SOURCE

TEST SET MODULE**

DOUBLER

YIG OSC

2-20 GHz

0-70dB

Step Attenuator

FP Amp Loop

µP

µP

µP

68030

S

S

b

b Loop

a Loop

a

a

b

1

1

1

1

2

2

S

S

HARM

GEN

L.O.

#1

L.O.

#2

L.O.

#3

REF OSC

10 MHz

I/O CONTROL

LOGIC

QUIET BUS

INTERFACE

&

CONTROL

A/D BUS

INTERFACE

&

CONTROL

EXTERNAL

KEYBOARD

INTERFACE

I/O PCB'S

FRONT

PANEL

INTERFACE

FLOPPY

DISK DRIVE

CONTROL

REAR PANEL

INTERFACE

&

CONTROL

FLOPPY

DISK

DRIVE

HARD

DISK

DRIVE

RAM

INTERFACE

CTL

GRAPHICS

PROCESSOR

PCB

INTERNAL

VGA

MONITOR

EXT VGA MONITOR

R.P.

LOGIC

CKTS

REAR

PANEL

PCB

GPIB

INTERFACE

VME BUS

MAIN PROCESSOR PCB

BBRAM

FRONT

PANEL

PCB

*

*

*

*

** For Models 37377A and 37397A, see Figures 5-3 and 5-4

Figure 7-1.

Overall Block Digram of 373XXA VNA System

*Model 37369A only