Xilinx LogiCore PCI v3.0 User Manual

Page 47

PCI v3.0.151 Getting Started Guide

47

UG157 August 31, 2005

Synplicity Synplify

R

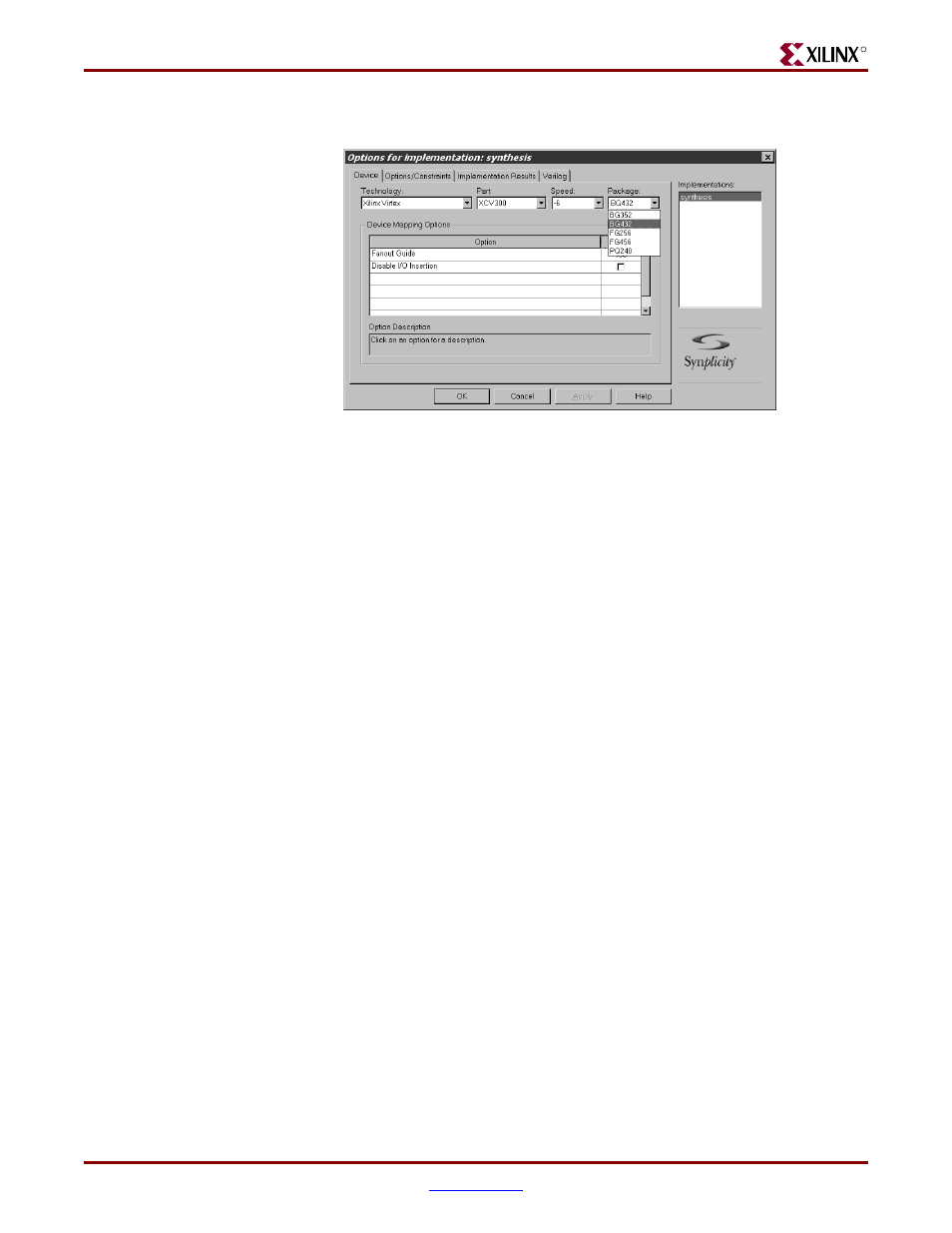

13. On the Device tab, set the Technology, Part, Speed, and Package options to reflect the

targeted device (a V300BG432-6 in this example). Be sure that Disable I/O Insertion is

deselected.

14. On the Options/Constraints tab, deselect Symbolic FSM Compiler (but leave Resource

Sharing selected) and set the Frequency to 66 MHz.

15. On the Implementation Results tab, deselect Write Vendor Constraint File.

16. Click OK to return to the main project window.

17. From the main project window, click Run.

Synplify synthesizes the design and writes out an optimized EDIF file. In the lower-

right corner of the window, the various stages or synthesis, such as Compiling or

Mapping, are displayed. When the process is complete, Done is displayed. Note that

Synplify may issue a number of warnings (are expected) about instantiated I/O cells

and attributes used for other synthesis tools.

Figure 5-11:

Options for Implementation: Device